# **Technical Note**

# Migrating from S29GL-N/P Devices to MT28EW NOR Flash Devices

# Introduction

This technical note describes the process for converting a system design from the Spansion<sup>®</sup> S29GL-N or S29GL-P device to the Micron<sup>®</sup> MT28EW single-level cell NOR Flash device, including 128Mb, 256Mb, 512Mb and 1Gb densities.

The higher reliability and performance characteristics of the MT28EW are ensured through advanced technology and product design improvements. The MT28EW features a large buffer size up to 512 words for advanced program performance. Erase performance is largely improved to meet all variable system design considerations. Moreover, MT28EW supports both ×8 and ×16 data bus for legacy controllers compatibility.

This document was written based on device information available at publication time. In case of inconsistency, information contained in the relevant MT28EW data sheet supersedes the information in this technical note. This document does not provide detailed device information. The standard density-specific device data sheet provides a complete description of device functionality, operating modes, and specifications.

# **Comparative Overview**

The MT28EW is compatible with the S29GL-P and S29GL-N 128Mb, 256Mb, 512Mb, and 1Gb devices, but features superior program and erase performance.

#### **Table 1: Part Number Comparison**

Notes 1 to 3 apply to the entire table

| Memory |                                     |                       | Part Numbers      |                   |

|--------|-------------------------------------|-----------------------|-------------------|-------------------|

| Size   | Package Type                        | Micron MT28EW         | Spansion S29GL-P  | Spansion S29GL-N  |

| 1Gb    | 56-pin TSOP                         | MT28EW01GABA1HJS-0SIT | S29GL01GPxxTxxx1x |                   |

|        | (14mm x 20mm) MT28EW01GABA1LJS-0SIT |                       | S29GL01GPxxTxxx2x |                   |

|        | 64-ball LBGA                        | MT28EW01GABA1HPC-0SIT | S29GL01GPxxFxxx1x |                   |

|        | (11mm x 13mm)                       | MT28EW01GABA1LPC-0SIT | S29GL01GPxxFxxx2x |                   |

| 512Mb  | 56-pin TSOP                         | MT28EW512ABA1HJS-0SIT | S29GL512PxxTxxx1x | S29GL512NxxTxlx1x |

|        | (14mm x 20mm)                       | MT28EW512ABA1LJS-0SIT | S29GL512PxxTxxx2x | S29GL512NxxTxlx2x |

|        | 64-ball LBGA                        | MT28EW512ABA1HPC-0SIT | S29GL512PxxFxxx1x | S29GL512NxxFxlx1x |

|        | (11mm x 13mm)                       | MT28EW512ABA1LPC-0SIT | S29GL512PxxTxxx2x | S29GL512NxxFxlx2x |

| 256Mb  | 56-pin TSOP                         | MT28EW256ABA1HJS-0SIT | S29GL256PxxTxxx1x | S29GL256NxxTxlx1x |

|        | (14mm x 20mm)                       | MT28EW256ABA1LJS-0SIT | S29GL256PxxTxxx2x | S29GL256NxxTxlx2x |

|        | 64-ball LBGA                        | MT28EW256ABA1HPC-0SIT | S29GL256PxxFxxx1x | S29GL256NxxFxlx1x |

|        | (11mm x 13mm)                       | MT28EW256ABA1LPC-0SIT | S29GL256PxxTxxx2x | S29GL256NxxFxlx2x |

| 128Mb  | 56-pin TSOP                         | MT28EW128ABA1HJS-0SIT | S29GL128PxxTxxx1x | S29GL128NxxTxlx1x |

|        | (14mm x 20mm)                       | MT28EW128ABA1LJS-0SIT | S29GL128PxxTxxx2x | S29GL128NxxTxlx2x |

|        | 64-ball LBGA                        | MT28EW128ABA1HPC-0SIT | S29GL128PxxFxxx1x | S29GL128NxxFxlx1x |

|        | (11mm x 13mm)                       | MT28EW128ABA1LPC-0SIT | S29GL128PxxTxxx2x | S29GL128NxxFxIx2x |

Notes: 1. To integrate line items on a variety of customer applications, the MT28EW device unifies the speed and voltage options.

- 2. For valid combination details, refer to www.micron.com/products and www.spansion.com.

- 3. Micron materials support the complete industrial temperature range.

#### **Table 2: Features Comparison**

| Feature                                | MT28EW                                                         | S29GL-P                                                                             | S29GL-N                                                                             | Notes |

|----------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|

| Process technology                     | 45nm single-level cell (SLC)<br>floating gate                  | 90nm MirrorBit                                                                      | 110nm MirrorBit                                                                     | 1     |

| Density                                | 128Mb                                                          | 128Mb                                                                               | 128Mb                                                                               |       |

|                                        | 256Mb                                                          | 256Mb                                                                               | 256Mb                                                                               |       |

|                                        | 512Mb                                                          | 512Mb                                                                               | 512Mb                                                                               |       |

|                                        | 1Gb                                                            | 1Gb                                                                                 |                                                                                     |       |

| Package                                | 64-ball LBGA<br>(11mm x 13mm),<br>56-pin TSOP<br>(14mm x 20mm) | 64-ball fortified BGA<br>(LAA064)<br>(11mm x 13mm),<br>56-pin TSOP<br>(14mm x 20mm) | 64-ball fortified BGA<br>(LAA064),<br>(11mm x 13mm)<br>56-pin TSOP<br>(14mm x 20mm) |       |

| Block architecture                     | Uniform 128KB                                                  | Uniform 128KB                                                                       | Uniform 128KB                                                                       |       |

| Data bus                               | x8/x16                                                         | x8/x16                                                                              | x8/x16                                                                              |       |

| Page read size                         | 16 words                                                       | 8 words                                                                             | 8 words                                                                             | 2     |

| Extended memory block                  | 128 words (8 + 120)                                            | 128 words (8 + 120)                                                                 | 128 words (8 + 120)                                                                 |       |

| Program write buffer size              | 256-word (x8 mode)<br>512-word (x16 mode)                      | 32-word                                                                             | 16-word                                                                             | 3     |

| V <sub>CC</sub> range                  | 2.7V to 3.6V                                                   | 2.7V to 3.6V                                                                        | 2.7V to 3.6V                                                                        |       |

| V <sub>CCQ</sub> range                 | 1.65~VCC                                                       | 1.65~VCC                                                                            | 1.65~VCC                                                                            |       |

| V <sub>PP</sub> accelerated (TYP)      | 9V                                                             | 12V                                                                                 | 12V                                                                                 | 4, 5  |

| CFI version                            | 1.3                                                            | 1.3                                                                                 | 1.3                                                                                 |       |

| High voltage auto select<br>(A9)       | No                                                             | Yes                                                                                 | Yes                                                                                 | 4, 6  |

| Individual block write pro-<br>tection | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| Permanent block locking<br>(OTP block) | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| Hardware protection                    | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| Unlock bypass                          | Yes                                                            | Yes                                                                                 | Yes                                                                                 | 4, 5  |

| Chip erase                             | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| RY/BY# pin                             | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| Blank check                            | Yes                                                            | No                                                                                  | No                                                                                  | 7     |

| Multiblock erase                       | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| Data polling                           | Yes                                                            | Yes                                                                                 | Yes                                                                                 |       |

| EFI CRC                                | Yes                                                            | No                                                                                  | No                                                                                  |       |

Notes: 1. MT28EW SLC floating gate technology provides improved performance and optimized quality and reliability.

2. Although the MT28EW features a larger page read size than the S29GL-P, no software updates are required during migration. However, software updates leveraging the

MT28EW device's larger page read buffer can yield improved read performance. To configure the MT28EW device's software, query CFI word address 4Ch.

- 3. Although the MT28EW features a larger program write buffer than either the S29GL-P or S29GL-N, no software updates are required during migration. However, software updates leveraging the MT28EW device's larger write buffer can yield improved performance. To configure the MT28EW device's software, query CFI word address 2Ah on the buffer size option, in either x8 or x16 mode (Refer to TN-13-07 for detail patch).

- 4. To avoid damaging the device, designs applying V<sub>PP</sub>/WP# voltages higher than 9.5V (MAX) should be modified. V<sub>PP</sub>/WP# should not remain at V<sub>PPH</sub> for more than 80 hours cumulative.

- By applying 9V (nominal) to the V<sub>PP</sub>/WP# pad, the MT28EW device supports V<sub>PPH</sub> unlock bypass, accelerated buffered programming, and accelerated chip erase operations. The 56-pin TSOP package pin 16 should be modified, and the 64-ball LBGA package ball B4 should be modified.

- 6. The MT28EW device does not support high voltage auto select on address A9. Instead, use the following command sequence to enter auto select mode: AAh/55h/90h. Applying 12 volts to address A9 or V<sub>PP</sub> may damage the device.

- 7. Refer to the Micron datasheet for detailed blank check command sets.

# **Hardware and Mechanical Considerations**

## **Packages and Ballouts**

The MT28EW device is available in 56-pin TSOP and 64-ball LBGA packages, both lead-free. For compatibility, the pin and ball assignments and the physical dimensions are equivalent to the S29GL-P and S29GL-N.

Systems migrating from a fortified BGA to an LBGA should not need to modify the reflow process in manufacturing.

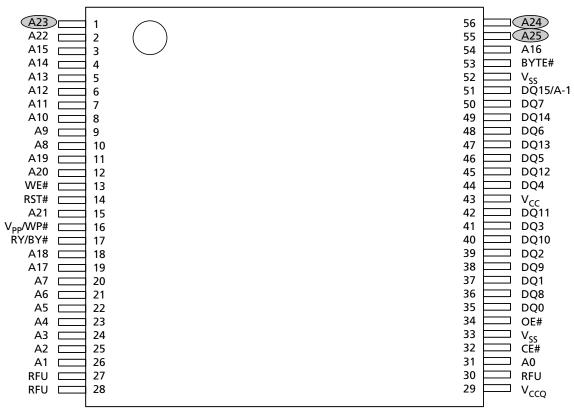

Figure 1: 56-Pin TSOP (Top View)

Notes: 1. A-1 is the least significant address bit in x8 mode.

- 2. A23 is valid for 256Mb and above; otherwise, it is RFU.

- 3. A24 is valid for 512Mb and above; otherwise, it is RFU.

- 4. A25 is valid for 1Gb; otherwise, it is RFU.

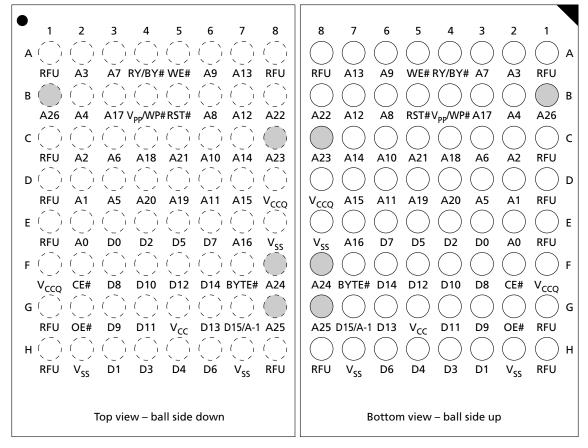

Figure 2: 64-Ball LBGA

- Notes: 1. A-1 is the least significant address bit in x8 mode.

- 2. A23 is valid for 256Mb and above; otherwise, it is RFU.

- 3. A24 is valid for 512Mb and above; otherwise, it is RFU.

- 4. A25 is valid for 1Gb; otherwise, it is RFU.

# Signals

## **Table 3: Signal Comparison**

| MT28EW               | S29GL-P & S29GL-N   | Туре         | Description                                     |

|----------------------|---------------------|--------------|-------------------------------------------------|

| A[MAX:0]             | A[MAX:0]            | Input        | Address inputs                                  |

| BYTE#                | BYTE#               | Input        | Byte/Word organization select cannot be floated |

| CE#                  | CE#                 | Input        | Chip enable                                     |

| OE#                  | OE#                 | Input        | Output enable                                   |

| RST#                 | RESET#              | Input        | Reset                                           |

| WE#                  | WE#                 | Input        | Write enable                                    |

| V <sub>PP</sub> /WP# | WP#/A <sub>CC</sub> | Input        | Acceleration power/write protect input          |

| DQ15/A-1             | DQ15/A-1            | I/O or Input | Data input/output or address input              |

| DQ[14:8]             | DQ[14:8]            | I/O          | Data inputs/outputs                             |

| DQ[7:0]              | DQ[7:0]             | I/O          | Data inputs/outputs                             |

| RY/BY#               | RY/BY#              | Output       | Ready/Busy                                      |

| V <sub>cc</sub>      | V <sub>cc</sub>     | Supply       | Supply voltage                                  |

| V <sub>CCQ</sub>     | V <sub>IO</sub>     | Supply       | Input/Output buffer supply voltage              |

| V <sub>SS</sub>      | V <sub>SS</sub>     | -            | Ground                                          |

| NC                   | NC                  | _            | No connect                                      |

## **Input/Output Capacitance**

#### **Table 4: Input/Output Capacitance Comparison**

|                  | MT28EW |     | S29 | GL-P | S290 |     |      |

|------------------|--------|-----|-----|------|------|-----|------|

| Parameter        | Min    | Мах | Min | Max  | Min  | Max | Unit |

| C <sub>IN</sub>  | 3      | 11  | 6   | 10   | 3.5  | 9   | pF   |

| C <sub>OUT</sub> | 3      | 7   | 10  | 12   | 3.9  | 12  | pF   |

Note: 1. C<sub>IN</sub> values for RESET, WP#/A<sub>CC</sub>, and CE# in the S29GL-N/P device are likely higher than the listed value.

## **Power Supply Decoupling**

Flash memory devices require careful power supply decoupling to prevent external transient noise from affecting device operations, and to prevent internally generated transient noise from affecting other devices in the system.

Ceramic chip capacitors of 0.01µF to 0.1µF should be used between each  $V_{CC}$ ,  $V_{CCQ}$ , and  $V_{PP}$  supply connection or system ground pin. These high-frequency, inherently low-inductance capacitors should be placed as close as possible to the device package, or on the opposite side of the printed circuit board close to the center of the device package footprint.

Larger electrolytic or tantulum bulk capacitors ( $4.7\mu$ F to  $33.0\mu$ F) should also be distributed as needed throughout the system to compensate for voltage sags and surges caused by circuit trace inductance.

Transient current magnitudes depend on the capacitive and inductive loading on the device's outputs. For best signal integrity and device performance, high-speed design rules should be used when designing the printed-circuit board. Final signal reflections (overshoot and undershoot) may vary by each system.

# **Software Considerations**

## **Command Set**

The MT28EW command set is fully compatible with that of S29GL-P and S29GL-N; therefore, no command change in the software is required. Micron provides some unique commands to support enhanced features such as EFI Blank check and EFI CRC functions.

# **Manufacturer ID and Auto Select Comparison**

On the MT28EW, the only way to use auto select mode is to issue an AUTO SELECT EN-TRY (90h) command. The S29GL-N/S29GL-P can use auto select mode via a high voltage (A9) method. Micron and Spansion have different manufacturer IDs; therefore, a slight modification in the software is required during migration.

The secure version of the MT28EW device does not have the same manufacturer ID as the standard version. To obtain the manufacturer ID of the secure version, contact your local Micron sales offices for MT28EW Security Addendum.

| Description                                         |                  | Address      | MT28EW | S29GL-P | S29GL-N |  |

|-----------------------------------------------------|------------------|--------------|--------|---------|---------|--|

| Manufacturer ID                                     |                  | (Base) + 00h | 0089h  | 0001h   | 0001h   |  |

| Device ID (cycle 1)                                 |                  | (Base) + 01h | 227Eh  | 227Eh   | 227Eh   |  |

| Device ID (cycle 2)                                 | 128Mb            | (Base) + 0Eh | 2221h  | 2221h   | 2221h   |  |

|                                                     | 256Mb            |              | 2222h  | 2222h   | 2222h   |  |

|                                                     | 512Mb            |              | 2223h  | 2223h   | 2223h   |  |

|                                                     | 1Gb              |              | 2228h  | 2228h   | -       |  |

| Device ID (cycle 3)                                 |                  | (Base) + 0Fh | 2201h  | 2201h   | 2201h   |  |

| Protection register indi-                           | Factory locked   | (Base) + 03h | 0099h  | 0099h   | 0098h   |  |

| cator – V <sub>PP</sub> /WP# locks<br>highest block | Factory unlocked |              | 0019h  | 0019h   | 0018h   |  |

| Protection register indi-                           | Factory locked   |              | 0089h  | 0089h   | 0088h   |  |

| cator – V <sub>PP</sub> /WP# locks<br>lowest block  | Factory unlocked |              | 0009h  | 0009h   | 0008h   |  |

| Block protection                                    | Protected        | (Base) + 02h | 0001h  | 0001h   | 0001h   |  |

|                                                     | Unprotected      |              | 0000h  | 0000h   | 0000h   |  |

### Table 5: Auto Select Comparison – Word Mode

# Unlock Bypass Mode

When the MT28EW device is in unlock bypass mode (AAh/55h/20h), the use of auto select mode (AAh/55h/90h) is not recommended. However, if auto select mode is used to read information when the device is in unlock bypass mode, an additional F0h command must be issued after AUTO SELECT READ to return to unlock bypass mode. Then, a subsequent auto select mode command must be issued to read out correct ID information.

This additional command is not required for S29GL device.

## TN-1335: Migrating S29GL-N/P to MT28EW NOR Flash Devices Software Considerations

In the following code example, the F0h command is written to any address during the first cycle:

```

FlashWrite(ANY ADDR, (uCPUBusType)CMD(0x00F0));

```

To access auto select information, use the following command sequence (AAh/55h/90h), but only when the device is not in unlock bypass mode. The following example demonstrates how to use auto select mode to read information from the device:

```

ReturnType ReadAutoSelectCode(uCPUBusType *addr, uCPUBusType *ucrCode)

{

/*Send the auto select command */

FlashWrite(ConvAddr(0x00555), (uCPUBusType)CMD(0x00AA)); /* first cycle */

FlashWrite(ConvAddr(0x002AA), (uCPUBusType)CMD(0x0055)); /* second cycle */

FlashWrite(ConvAddr(0x00555), (uCPUBusType)CMD(0x0090)); /* third cycle */

/* Read the code */

*ucrCode = FlashRead(addr);

/* Return to read array mode */

FlashWrite(ANY_ADDR, (uCPUBusType)CMD(0x00F0); /* first cycle: write 0x00F0 to any

address */

/* Check flash response (more flashes could give different results) */

return FlashResponseIntegrityCheck(ucrCode);

}

```

## **EXIT PROTECTION COMMAND SET**

The Micron device provides three software protection modes: volatile, nonvolatile, and password protection. The device is shipped with all blocks unprotected. On first use, the device can be activated in either the nonvolatile protection or password protection mode.

The EXIT PROTECTION COMMAND SET (90/00h) command is used to exit the lock register, password protection, nonvolatile protection, volatile protection, and nonvolatile protection bit lock bit command set modes and return the device to read mode. The second cycle for the Micron device must be 00h while the Spansion device may accept other command codes to exit the above modes.

# **CFI Comparison**

CFI differences exist between MT28EW and S29GL-P/S29GL-N due to device features and performance characteristics.

#### **Table 6: CFI Comparison**

| Address | Description                                                            | MT28EW | S29GL-P | S29GL-N | Notes |

|---------|------------------------------------------------------------------------|--------|---------|---------|-------|

| 1Dh     | V <sub>PPH</sub> (programming) supply minimum<br>PROGRAM/ERASE voltage | 0085   | 0000    | 0000    |       |

|         | Bits[7:4] hex value in volts                                           |        |         |         |       |

|         | Bits[3:0] BCD value in 100mV                                           |        |         |         |       |

#### **Table 6: CFI Comparison (Continued)**

| Address | Description                                                                               | MT28     | BEW         | S29   | GL-P | S29GL-N    | Notes |

|---------|-------------------------------------------------------------------------------------------|----------|-------------|-------|------|------------|-------|

| 1Eh     | V <sub>PPH</sub> (programming) supply maximum<br>PROGRAM/ERASE voltage                    | 009      | 95          | 00    | 00   | 0000       |       |

|         | Bits[7:4] hex value in volts                                                              |          |             |       |      |            |       |

|         | Bits[3:0] BCD value in 100mV                                                              |          |             |       |      |            |       |

| 1Fh     | Typical timeout for single byte/word<br>PROGRAM = 2 <sup>n</sup> µs                       | 000      | 05          | 0006  |      | 0007       |       |

| 20h     | Typical timeout for maximum size BUF-<br>FER PROGRAM = $2^{n}\mu$ s                       | 0009     |             | 00    | 06   | 0007       | 1     |

| 21h     | Typical timeout for individual BLOCK<br>ERASE = 2 <sup>n</sup> ms                         | 0008     |             | 00    | 09   | 000A       |       |

| 22h     | Typical timeout for full-chip ERASE =                                                     | 128Mb    | 000F        | 128Mb | 0010 | 0000 (not  |       |

|         | 2 <sup>n</sup> ms                                                                         | 256Mb    | 0010        | 256Mb | 0011 | supported) |       |

|         |                                                                                           | 512Mb    | 0011        | 512Mb | 0012 |            |       |

|         |                                                                                           | 1Gb      | 0012        | 1Gb   | 0013 |            |       |

| 23h     | Maximum timeout for byte/word PRO-<br>GRAM = $2^n$ times typical timeout                  | 000      | 03          | 0003  |      | 0003       |       |

| 24h     | Maximum timeout for BUFFER PRO-<br>GRAM = $2^n$ times typical timeout                     | 0002     |             | 00    | 0005 |            |       |

| 25h     | Maximum timeout per individual<br>BLOCK ERASE = 2 <sup>n</sup> times typical time-<br>out | 0003     |             | 0003  |      | 0004       |       |

| 26h     | Maximum timeout for chip ERASE = 2 <sup>n</sup><br>times typical timeout                  | 000      | 03          | 0002  |      | 0000       |       |

| 2Ah     | Maximum number of bytes in multiple-                                                      | x8 mode  | 08          | 00    | 06   | 0005       |       |

|         | byte write = 2 <sup>n</sup>                                                               | x16 mode | 000A        |       |      |            |       |

| 45h     | Address-sensitive unlock (bits[1:0])                                                      | 00       | 1C          | 00    | 14   | 0010       |       |

|         | 0 = required, 1 = not required                                                            |          |             |       |      |            |       |

|         | Silicon revision number (bits[7:2])                                                       |          |             |       |      |            |       |

| 4C      | Page mode                                                                                 | 000      | 03          | 00    | 02   | 0002       |       |

|         | 00 = not supported                                                                        |          |             |       |      |            |       |

|         | 01 = 4-word page                                                                          |          |             |       |      |            |       |

|         | 02 = 8-word page                                                                          |          |             |       |      |            |       |

|         | 03 = 16-word page                                                                         |          |             |       |      |            |       |

| 4D      | V <sub>PPH</sub> supply minimum PROGRAM/<br>ERASE voltage                                 | 008      | 0085h 00B5h |       | 35h  | 00B5h      |       |

|         | Bits[7:4] hex value in volts                                                              | ]        |             |       |      |            |       |

|         | Bits[3:0] BCD value in 100mV                                                              | ]        |             |       |      |            |       |

### **Table 6: CFI Comparison (Continued)**

| Address | Description                                               | MT28EW | S29GL-P | S29GL-N | Notes |

|---------|-----------------------------------------------------------|--------|---------|---------|-------|

| 4E      | V <sub>PPH</sub> supply maximum PROGRAM/<br>ERASE voltage | 0095h  | 00C5h   | 00C5h   |       |

|         | Bits[7:4] hex value in volts                              |        |         |         |       |

|         | Bits[3:0] BCD value in 100mV                              |        |         |         |       |

Note: 1. S29GL-N/P device defines this value as a minimum instead of a maximum; that is, the typical timeout for a minimum size buffer write =  $2^n \mu s$

# **Performance Comparison**

The MT28EW features significantly improved program and erase performance.

#### Table 7: Program and Erase Performance Comparison (Word Mode)

|                                   | MT2               | 8EW               | S290               | GL-P | S290               | iL-N |      |

|-----------------------------------|-------------------|-------------------|--------------------|------|--------------------|------|------|

| Parameter                         | Тур               | Мах               | Тур                | Мах  | Тур                | Мах  | Unit |

| Block Erase                       | _                 | 1                 |                    |      |                    |      | -    |

| Block erase                       | 200               | 1100              | 500                | 3500 | 500                | 3500 | ms   |

| Accelerated chip Erase            |                   | 1                 |                    |      | -i i               |      | 1    |

| 128Mb                             | 23                | -                 | -                  | -    | -                  | -    | s    |

| 256Mb                             | 47                | -                 | -                  | -    | -                  | -    |      |

| 512Mb                             | 95                | -                 | -                  | -    | -                  | -    |      |

| 1Gb                               | 190               | -                 | -                  | -    | -                  | -    |      |

| Chip Erase                        |                   | 1                 |                    |      | -i i               |      | 1    |

| 128Mb                             | 26                | _                 | 64                 | _    | 64                 | _    | s    |

| 256Mb                             | 52                | _                 | 128                | _    | 128                | _    |      |

| 512Mb                             | 104               | _                 | 256                | _    | 256                | _    |      |

| 1Gb                               | 208               | _                 | 512                | _    | _                  | _    |      |

| Program/Erase Suspend             |                   |                   | · · · · ·          |      | - <b>-</b>         |      | •    |

| Erase suspend latency time        | 15                | 20                | 5                  | 20   | 5                  | 20   | μs   |

| Program suspend latency time      | 10                | 15                | 5                  | 15   | 5                  | 20   |      |

| Program, x16                      |                   |                   | · · · · ·          |      | - <b>-</b>         |      | •    |

| Single word                       | 25                | 200               | 60                 | 480  | 60                 | _    | μs   |

| Write-to-buffer (16 words)        | 50<br>(0.64MB/s)  | -                 | -                  | -    | 240<br>(0.07 MB/s) | -    |      |

| Write-to-buffer (32 words)        | 92<br>(0.7 MB/s)  | 460               | 480<br>(0.07 MB/s) | _    | -                  | -    |      |

| Write-to-buffer (64 words)        | 117<br>(1.1 MB/s) | 600               | -                  | -    | -                  | -    |      |

| Write-to-buffer (128 words)       | 171<br>(1.5 MB/s) | 900               | -                  | _    | -                  | _    |      |

| Write-to-buffer (256 words)       | 285<br>(1.8 MB/s) | 1500              | -                  | -    | -                  | -    |      |

| Write-to-buffer (512 words)       | 512<br>(2.0 MB/s) | 2000              | -                  | _    | -                  | _    |      |

| Accelerated full buffered program | -                 | 410<br>(2.5 MB/s) | -                  | _    | -                  | _    |      |

#### Table 8: Read AC Performance Comparison – 3V

|                               | Symbol           |                   | MT2 | 8EW | S29 | GL-P   | S290 | GL-N   |      |       |

|-------------------------------|------------------|-------------------|-----|-----|-----|--------|------|--------|------|-------|

| Parameter                     | Legacy           | JEDEC             | Min | Max | Min | Max    | Min  | Мах    | Unit | Notes |

| Address valid to output valid | <sup>t</sup> ACC | <sup>t</sup> AVQV | -   | 95  | -   | 90–110 | -    | 90–110 | ns   | 1     |

| Page address access           | <sup>t</sup> APA | -                 | -   | 20  | _   | 25     | -    | 25     | ns   |       |

| OE# LOW to output valid       | <sup>t</sup> OE  | <sup>t</sup> GLQV | -   | 25  | _   | 25     | -    | 25     | ns   |       |

Note: 1. For MT28EW, maximum value is 70ns for 128M/256M only.

#### **Table 9: Power Consumption Comparison**

|                                          |                  | MT2 | 8EW | S29 | GL-P | S29 | GL-N |      |

|------------------------------------------|------------------|-----|-----|-----|------|-----|------|------|

| Parameter                                | Symbol           | Тур | Мах | Тур | Мах  | Тур | Max  | Unit |

| Read                                     |                  |     |     |     |      |     |      |      |

| V <sub>CC</sub> random<br>read current   | I <sub>CC1</sub> | 26  | 31  | 30  | 55   | 30  | 50   | mA   |

| V <sub>CC</sub> page read<br>curent      | I <sub>CC1</sub> | 12  | 16  | 1   | 10   | 1   | 10   |      |

| Standby                                  |                  |     |     |     |      |     | •    |      |

| 1Gb Vcc standby<br>current               | I <sub>CC2</sub> | 75  | 230 | 1   | 5    | 1   | 5    | μA   |

| 512Mb V <sub>CC</sub><br>standby current |                  | 70  | 200 | 1   | 5    | 1   | 5    |      |

| 256Mb V <sub>CC</sub><br>standby current | I <sub>CC2</sub> | 65  | 136 | 1   | 5    | 1   | 5    | -    |

| 128Mb V <sub>CC</sub><br>standby current |                  | 50  | 120 | 1   | 5    | 1   | 5    | -    |

| Program/Erase                            |                  |     |     |     |      |     | •    |      |

| V <sub>CC</sub> erase cur-<br>rent       | I <sub>CC3</sub> | 35  | 50  | 50  | 90   | 50  | 90   | mA   |

| V <sub>CC</sub> program<br>current       | I <sub>CC3</sub> | 35  | 50  | 50  | 90   | 50  | 90   |      |

# **Power-on and Reset Timings**

Because many of the more common processors support the MT28EW timings, there should be no adverse effect from timing differences.

#### **Table 10: Reset Timing Comparison**

|                                                  | Syn                | Symbol                                  |     | 8EW | S29  | GL-P | S29GL-N |     |      |

|--------------------------------------------------|--------------------|-----------------------------------------|-----|-----|------|------|---------|-----|------|

| Condition/Parameter                              | Legacy             | JEDEC                                   | Min | Мах | Min  | Мах  | Min     | Мах | Unit |

| V <sub>CC</sub> power valid to RST# HIGH         | <sup>t</sup> VCS   | <sup>t</sup> VCHPH                      | 300 | -   | 35   | -    | 50      | -   | μs   |

| RST# LOW to read mode during<br>program or erase | <sup>t</sup> READY | <sup>t</sup> PLRH                       | _   | 25  | -    | 35   | -       | 20  | μs   |

| RST# pulse width                                 | <sup>t</sup> RP    | <sup>t</sup> PLPH                       | 100 | -   | 3500 | -    | 500     | -   | ns   |

| RST# HIGH to CE# LOW, OE# LOW                    | <sup>t</sup> RH    | <sup>t</sup> PHEL,<br><sup>t</sup> PHGL | 50  | -   | 200  | -    | 50      | _   | ns   |

| RY/BY# HIGH to CE# LOW, OE#<br>LOW               | <sup>t</sup> RB    | <sup>t</sup> RHEL,<br><sup>t</sup> RHGL | 0   | _   | 0    | -    | 0       | -   | ns   |

# **Related Information**

#### Table 11: Document List

Document/Tool

# Parallel NOR Flash Embedded Memory MT28EW datasheet (all densities)

S29GL-P\_00: SPANSION<sup>®</sup> MirrorBit<sup>®</sup> S29GL-P 1-Gbit, 512-Mbit, 256-Mbit, 128-Mbit 3.0 Volt-only Page Mode Flash Memory datasheet

S29GL-N\_00: SPANSION<sup>®</sup> MirrorBit<sup>®</sup> S29GL-N 512-Mbit, 256-Mbit, 128-Mbit 3.0 Volt- only Page Mode Flash Memory datasheet

TN-13-12: Software Driver for M29EW NOR Flash Memory

Application Note 309046: Power Loss Recovery for NOR Flash Memory

TN-13-30: System Design Considerations with Micron Flash Memory

TN-13-07: Patching the Linux Kernel and U-Boot for Micron M29 Flash Memory

Notes: 1. Contact your local Micron or distribution sales office to request additional documentation.

2. Visit http://www.micron.com for technical documentation.

# **Revision History**

## Rev. B - 09/15

- Updated performance based on latest datasheet

- Removed 2Gb density information

## Rev. A – 05/14

• Initial release

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000 www.micron.com/products/support Sales inquiries: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.