## DDR4 SDRAM VLP UDIMM

#### MTA9ADF1G72AZ - 8GB

#### **Features**

- DDR4 functionality and operations supported as defined in the component data sheet

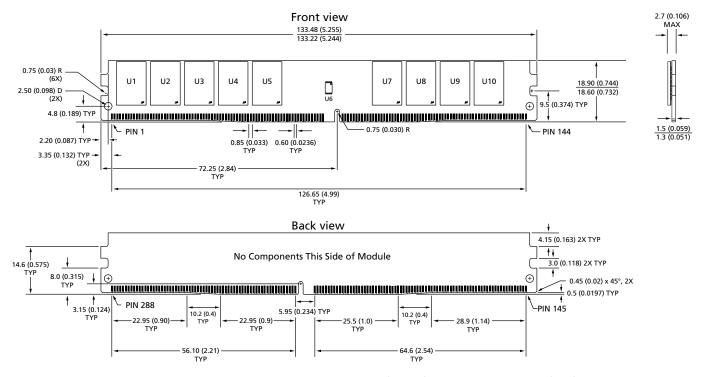

- 288-pin, unbuffered very low profile dual in-line memory module (VLP UDIMM)

- Fast data transfer rate: PC4-3200, PC4-2666

- 8GB (1 Gig x 72)

- $V_{DD} = 1.20 V (NOM)$

- $V_{PP} = 2.5V (NOM)$

- $V_{DDSPD} = 2.5V (NOM)$

- Supports ECC error detection and correction

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Low-power auto self refresh (LPASR)

- Data bus inversion (DBI) for data bus

- On-die V<sub>REFDO</sub> generation and calibration

- Single-rank

- On-board I<sup>2</sup>C temperature sensor with integrated serial presence-detect (SPD) EEPROM

- 16 internal banks; 4 groups of 4 banks each

- Fixed burst chop (BC) of 4 and burst length (BL) of 8 via the mode register set (MRS)

- Selectable BC4 or BL8 on-the-fly (OTF)

- Gold edge contacts

- · Halogen-free

- Fly-by topology

- Terminated control, command, and address bus

Figure 1: 288-Pin VLP UDIMM (R/C ZZ)

| Options                                                                 | Marking |

|-------------------------------------------------------------------------|---------|

| Operating temperature                                                   |         |

| <ul><li>Commercial</li></ul>                                            | None    |

| $(0^{\circ}\text{C} \le \text{T}_{\text{OPER}} \le 95^{\circ}\text{C})$ |         |

| • Package                                                               |         |

| <ul> <li>288-pin DIMM (halogen-free)</li> </ul>                         | Z       |

| • Frequency/CAS latency                                                 |         |

| - 0.625ns @ CL = 22 (DDR4-3200)                                         | -3G2    |

| - 0.75ns @ CL = 19 (DDR4-2666)                                          | -2G6    |

#### **Table 1: Key Timing Parameters**

| Speed | PC4- | 24            | 20\ 18\ 16\ 14\ 12\ 10\<br>24 22 21 19 17 15 13 11 9 |      |               |               |               |               |               |            |                               | <sup>t</sup> RP<br>ns         | <sup>t</sup> RC<br>ns         |

|-------|------|---------------|------------------------------------------------------|------|---------------|---------------|---------------|---------------|---------------|------------|-------------------------------|-------------------------------|-------------------------------|

| -3G2  | 3200 | 3200,<br>2933 | 3200,<br>2933                                        | 2933 | 2666\<br>2666 | 2400\<br>2400 | 2133\<br>2133 | 1866\<br>1866 | 1600\<br>1600 | 1333\<br>- | 13.75                         | 13.75                         | 45.75                         |

| -2G9  | 2933 | _             | 2933                                                 | 2933 | 2666\<br>2666 | 2400\<br>2400 | 2133\<br>2133 | 1866\<br>1866 | 1600\<br>1600 | 1333\<br>- | 14.32<br>(13.75) <sup>1</sup> | 14.32<br>(13.75) <sup>1</sup> | 46.32<br>(45.75) <sup>1</sup> |

| -2G6  | 2666 | _             | -                                                    | ı    | 2666\<br>2666 | 2400\<br>2400 | 2133\<br>2133 | 1866\<br>1866 | 1600\<br>1600 | 1333\<br>- | 14.25<br>(13.75) <sup>1</sup> | 14.25<br>(13.75) <sup>1</sup> | 46.25<br>(45.75) <sup>1</sup> |

**Table 1: Key Timing Parameters (Continued)**

| <b>T</b> 0     |      | Data Rate (MT/s) CL = |                                                      |   |   |               |               |               |               |            |                               |                               |                               |

|----------------|------|-----------------------|------------------------------------------------------|---|---|---------------|---------------|---------------|---------------|------------|-------------------------------|-------------------------------|-------------------------------|

| Speed<br>Grade | PC4- | 24                    | 20\ 18\ 16\ 14\ 12\ 10\<br>24 22 21 19 17 15 13 11 9 |   |   |               |               |               |               |            | <sup>t</sup> RCD<br>ns        | <sup>t</sup> RP<br>ns         | <sup>t</sup> RC<br>ns         |

| -2G3           | 2400 | _                     | _                                                    | _ | _ | 2400\<br>2400 | 2133\<br>2133 | 1866\<br>1866 | 1600\<br>1600 | 1333\<br>- | 14.16<br>(13.75) <sup>1</sup> | 14.16<br>(13.75) <sup>1</sup> | 46.16<br>(45.75) <sup>1</sup> |

| -2G1           | 2133 | ı                     | 2122) 1966) 1600) 1222)                              |   |   |               |               |               |               |            |                               | 14.06<br>(13.5) <sup>1</sup>  | 47.06<br>(46.5) <sup>1</sup>  |

Note: 1. Down-bin timing, refer to component data sheet Speed Bin Tables for details.

#### **Table 2: Addressing**

| Parameter                     | 8GB                       |

|-------------------------------|---------------------------|

| Row address                   | 64K A[15:0]               |

| Column address                | 1K A[9:0]                 |

| Device bank group address     | 4 BG[1:0]                 |

| Device bank address per group | 4 BA[1:0]                 |

| Device configuration          | 8Gb (1 Gig x 8), 16 banks |

| Module rank address           | CS0_n                     |

#### Table 3: Part Numbers and Timing Parameters - 8GB Modules

Base device: MT40A1G8, 18Gb DDR4 SDRAM

| Part Number <sup>2</sup> | Module<br>Density | Configuration | Module<br>Bandwidth | Memory Clock/<br>Data Rate | Clock Cycles<br>(CL- <sup>t</sup> RCD- <sup>t</sup> RP) |

|--------------------------|-------------------|---------------|---------------------|----------------------------|---------------------------------------------------------|

| MTA9ADF1G72AZ-3G2        | 8GB               | 1 Gig x 72    | 25.6 GB/s           | 0.625ns/3200 MT/s          | 22-22-22                                                |

| MTA9ADF1G72AZ-2G6        | 8GB               | 1 Gig x 72    | 21.3 GB/s           | 0.75ns/2666 MT/s           | 19-19-19                                                |

Notes: 1. The data sheet for the base device can be found at micron.com.

2. All part numbers end with a two-place code (not shown) that designates component and PCB revisions. Consult factory for current revision codes. Example: MTA9ADF1G72AZ-3G2<u>J1</u>.

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Features

#### **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Pin Assignments

## **Pin Assignments**

The pin assignment table below is a comprehensive list of all possible pin assignments for DDR4 UDIMM modules. See Functional Block Diagram for pins specific to this module.

**Table 4: Pin Assignments**

|     |                         | 288 | -Pin DDR4               | UDIN | /IM Front       |     |                         | 288-Pin DDR4 UDIMM Back |                    |     |                 |     |                 |     |                 |

|-----|-------------------------|-----|-------------------------|------|-----------------|-----|-------------------------|-------------------------|--------------------|-----|-----------------|-----|-----------------|-----|-----------------|

| Pin | Symbol                  | Pin | Symbol                  | Pin  | Symbol          | Pin | Symbol                  | Pin                     | Symbol             | Pin | Symbol          | Pin | Symbol          | Pin | Symbol          |

| 1   | NC                      | 37  | V <sub>SS</sub>         | 73   | V <sub>DD</sub> | 109 | V <sub>SS</sub>         | 145                     | NC                 | 181 | DQ29            | 217 | V <sub>DD</sub> | 253 | DQ41            |

| 2   | V <sub>SS</sub>         | 38  | DQ24                    | 74   | CK0_t           | 110 | DM5_n/<br>DBI5_n,<br>NC | 146                     | V <sub>REFCA</sub> | 182 | V <sub>SS</sub> | 218 | CK1_t           | 254 | V <sub>SS</sub> |

| 3   | DQ4                     | 39  | V <sub>SS</sub>         | 75   | CK0_c           | 111 | NC                      | 147                     | V <sub>SS</sub>    | 183 | DQ25            | 219 | CK1_c           | 255 | DQS5_c          |

| 4   | V <sub>SS</sub>         | 40  | DM3_n/<br>DBI3_n,<br>NC | 76   | V <sub>DD</sub> | 112 | V <sub>SS</sub>         | 148                     | DQ5                | 184 | V <sub>SS</sub> | 220 | V <sub>DD</sub> | 256 | DQS5_t          |

| 5   | DQ0                     | 41  | NC                      | 77   | V <sub>TT</sub> | 113 | DQ46                    | 149                     | $V_{SS}$           | 185 | DQS3_c          | 221 | $V_{TT}$        | 257 | $V_{SS}$        |

| 6   | V <sub>SS</sub>         | 42  | V <sub>SS</sub>         | 78   | EVENT_n,<br>NF  | 114 | V <sub>SS</sub>         | 150                     | DQ1                | 186 | DQS3_t          | 222 | PARITY          | 258 | DQ47            |

| 7   | DM0_n/<br>DBI0_n,<br>NC | 43  | DQ30                    | 79   | A0              | 115 | DQ42                    | 151                     | V <sub>SS</sub>    | 187 | V <sub>SS</sub> | 223 | V <sub>DD</sub> | 259 | V <sub>SS</sub> |

| 8   | NC                      | 44  | V <sub>SS</sub>         | 80   | V <sub>DD</sub> | 116 | V <sub>SS</sub>         | 152                     | DQS0_c             | 188 | DQ31            | 224 | BA1             | 260 | DQ43            |

| 9   | V <sub>SS</sub>         | 45  | DQ26                    | 81   | BA0             | 117 | DQ52                    | 153                     | DQS0_t             | 189 | V <sub>SS</sub> | 225 | A10_AP          | 261 | V <sub>SS</sub> |

| 10  | DQ6                     | 46  | V <sub>SS</sub>         | 82   | RAS_n/<br>A16   | 118 | V <sub>SS</sub>         | 154                     | V <sub>SS</sub>    | 190 | DQ27            | 226 | $V_{DD}$        | 262 | DQ53            |

| 11  | V <sub>SS</sub>         | 47  | CB4/ NC                 | 83   | V <sub>DD</sub> | 119 | DQ48                    | 155                     | DQ7                | 191 | V <sub>SS</sub> | 227 | NC              | 263 | V <sub>SS</sub> |

| 12  | DQ2                     | 48  | V <sub>SS</sub>         | 84   | CS0_n           | 120 | V <sub>SS</sub>         | 156                     | V <sub>SS</sub>    | 192 | CB5, NC         | 228 | WE_n/<br>A14    | 264 | DQ49            |

| 13  | V <sub>SS</sub>         | 49  | CB0/ NC                 | 85   | V <sub>DD</sub> | 121 | DM6_n/<br>DBI6_n,<br>NC | 157                     | DQ3                | 193 | V <sub>SS</sub> | 229 | V <sub>DD</sub> | 265 | V <sub>SS</sub> |

| 14  | DQ12                    | 50  | V <sub>SS</sub>         | 86   | CAS_n/<br>A15   | 122 | NC                      | 158                     | V <sub>SS</sub>    | 194 | CB1, NC         | 230 | NC              | 266 | DQS6_c          |

| 15  | V <sub>SS</sub>         | 51  | DM8_n/<br>DBI8_n,<br>NC | 87   | ODT0            | 123 | V <sub>SS</sub>         | 159                     | DQ13               | 195 | V <sub>SS</sub> | 231 | $V_{DD}$        | 267 | DQS6_t          |

| 16  | DQ8                     | 52  | NC                      | 88   | V <sub>DD</sub> | 124 | DQ54                    | 160                     | V <sub>SS</sub>    | 196 | DQS8_c          | 232 | A13             | 268 | V <sub>SS</sub> |

| 17  | V <sub>SS</sub>         | 53  | V <sub>SS</sub>         | 89   | CS1_n,<br>NC    | 125 | V <sub>SS</sub>         | 161                     | DQ9                | 197 | DQS8_t          | 233 | $V_{DD}$        | 269 | DQ55            |

| 18  | DMI_n/<br>DBI1_n,<br>NC | 54  | CB6/<br>DBI8_n,<br>NC   | 90   | V <sub>DD</sub> | 126 | DQ50                    | 162                     | V <sub>SS</sub>    | 198 | V <sub>SS</sub> | 234 | NC              | 270 | V <sub>SS</sub> |

| 19  | NC                      | 55  | V <sub>SS</sub>         | 91   | ODT1,<br>NC     | 127 | V <sub>SS</sub>         | 163                     | DQS1_c             | 199 | CB7, NC         | 235 | NC              | 271 | DQ51            |

| 20  | V <sub>SS</sub>         | 56  | CB2/ NC                 | 92   | $V_{DD}$        | 128 | DQ60                    | 164                     | DQS1_t             | 200 | $V_{SS}$        | 236 | $V_{DD}$        | 272 | $V_{SS}$        |

| 21  | DQ14                    | 57  | V <sub>SS</sub>         | 93   | NC              | 129 | V <sub>SS</sub>         | 165                     | V <sub>SS</sub>    | 201 | CB3, NC         | 237 | NC              | 273 | DQ61            |

| 22  | V <sub>SS</sub>         | 58  | RESET_n                 | 94   | V <sub>SS</sub> | 130 | DQ56                    | 166                     | DQ15               | 202 | V <sub>SS</sub> | 238 | SA2             | 274 | V <sub>SS</sub> |

| 23  | DQ10                    | 59  | $V_{DD}$                | 95   | DQ36            | 131 | V <sub>SS</sub>         | 167                     | V <sub>SS</sub>    | 203 | CKE1,<br>NC     | 239 | V <sub>SS</sub> | 275 | DQ57            |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Pin Assignments

#### **Table 4: Pin Assignments (Continued)**

|     |                         | 288 | -Pin DDR4 | UDIN | IM Front                |     |                         | 288-Pin DDR4 UDIMM Back |                 |     |          |     |                 |     |                    |

|-----|-------------------------|-----|-----------|------|-------------------------|-----|-------------------------|-------------------------|-----------------|-----|----------|-----|-----------------|-----|--------------------|

| Pin | Symbol                  | Pin | Symbol    | Pin  | Symbol                  | Pin | Symbol                  | Pin                     | Symbol          | Pin | Symbol   | Pin | Symbol          | Pin | Symbol             |

| 24  | V <sub>SS</sub>         | 60  | CKE0      | 96   | V <sub>SS</sub>         | 132 | DM7_n/<br>DBI7_n,<br>NC | 168                     | DQ11            | 204 | $V_{DD}$ | 240 | DQ37            | 276 | V <sub>SS</sub>    |

| 25  | DQ20                    | 61  | $V_{DD}$  | 97   | DQ32                    | 133 | NC                      | 169                     | $V_{SS}$        | 205 | NC       | 241 | $V_{SS}$        | 277 | DQS7_c             |

| 26  | V <sub>SS</sub>         | 62  | ACT_n     | 98   | $V_{SS}$                | 134 | $V_{SS}$                | 170                     | DQ21            | 206 | $V_{DD}$ | 242 | DQ33            | 278 | DQS7_t             |

| 27  | DQ16                    | 63  | BG0       | 99   | DM4_n/<br>DBI4_n,<br>NC | 135 | DQ62                    | 171                     | V <sub>SS</sub> | 207 | BG1      | 243 | V <sub>SS</sub> | 279 | V <sub>SS</sub>    |

| 28  | V <sub>SS</sub>         | 64  | $V_{DD}$  | 100  | NC                      | 136 | $V_{SS}$                | 172                     | DQ17            | 208 | ALERT_n  | 244 | DQS4_c          | 280 | DQ63               |

| 29  | DM2_n/<br>DBI2_n,<br>NC | 65  | A12/BC_n  | 101  | V <sub>SS</sub>         | 137 | DQ58                    | 173                     | V <sub>SS</sub> | 209 | $V_{DD}$ | 245 | DQS4_t          | 281 | V <sub>SS</sub>    |

| 30  | NC                      | 66  | A9        | 102  | DQ38                    | 138 | V <sub>SS</sub>         | 174                     | DQS2_c          | 210 | A11      | 246 | V <sub>SS</sub> | 282 | DQ59               |

| 31  | V <sub>SS</sub>         | 67  | $V_{DD}$  | 103  | V <sub>SS</sub>         | 139 | SA0                     | 175                     | DQS2_t          | 211 | A7       | 247 | DQ39            | 283 | V <sub>SS</sub>    |

| 32  | DQ22                    | 68  | A8        | 104  | DQ34                    | 140 | SA1                     | 176                     | V <sub>SS</sub> | 212 | $V_{DD}$ | 248 | V <sub>SS</sub> | 284 | V <sub>DDSPD</sub> |

| 33  | V <sub>SS</sub>         | 69  | A6        | 105  | V <sub>SS</sub>         | 141 | SCL                     | 177                     | DQ23            | 213 | A5       | 249 | DQ35            | 285 | SDA                |

| 34  | DQ18                    | 70  | $V_{DD}$  | 106  | DQ44                    | 142 | V <sub>PP</sub>         | 178                     | V <sub>SS</sub> | 214 | A4       | 250 | V <sub>SS</sub> | 286 | V <sub>PP</sub>    |

| 35  | V <sub>SS</sub>         | 71  | A3        | 107  | V <sub>SS</sub>         | 143 | $V_{PP}$                | 179                     | DQ19            | 215 | $V_{DD}$ | 251 | DQ45            | 287 | V <sub>PP</sub>    |

| 36  | DQ28                    | 72  | A1        | 108  | DQ40                    | 144 | NC                      | 180                     | V <sub>SS</sub> | 216 | A2       | 252 | $V_{SS}$        | 288 | $V_{PP}$           |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Pin Descriptions

## **Pin Descriptions**

The pin description table below is a comprehensive list of all possible pins for DDR4 modules. All pins listed may not be supported on this module. See the Functional Block Diagram located in the module MPN data sheet addendum for pins specific to the module

**Table 5: Pin Descriptions**

| Symbol                                 | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ax                                     | Input | Address inputs: Provide the row address for ACTIVATE commands and the column address for READ/WRITE commands in order to select one location out of the memory array in the respective bank (A10/AP, A12/BC_n, WE_n/A14, CAS_n/A15, and RAS_n/A16 have additional functions; see individual entries in this table). The address inputs also provide the op-code during the MODE REGISTER SET command. A17 is only defined for x4 SDRAM.                                                                                                                                                                                                                                                                                       |

| A10/AP                                 | Input | Auto precharge: A10 is sampled during READ and WRITE commands to determine whether an auto precharge should be performed on the accessed bank after a READ or WRITE operation (HIGH = auto precharge; LOW = no auto precharge). A10 is sampled during a PRECHARGE command to determine whether the precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by the bank group and bank addresses.                                                                                                                                                                                                                                                          |

| A12/BC_n                               | Input | <b>Burst chop:</b> A12/BC_n is sampled during READ and WRITE commands to determine if burst chop (on-the-fly) will be performed (HIGH = no burst chop; LOW = burst chopped). See Command Truth Table in the DDR4 component data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACT_n                                  | Input | <b>Command input:</b> ACT_n defines the ACTIVATE command being entered along with CS_n. The input into RAS_n/A16, CAS_n/A15, and WE_n/A14 are considered as row address A16, A15, and A14. See Command Truth Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BAx                                    | Input | <b>Bank address inputs:</b> Define the bank (with a bank group) to which an ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. Also determine which mode register is to be accessed during a MODE REGISTER SET command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BGx                                    | Input | <b>Bank group address inputs:</b> Define the bank group to which a REFRESH, ACTIVATE, READ, WRITE, or PRECHARGE command is being applied. Also determine which mode register is to be accessed during a MODE REGISTER SET command. BG[1:0] are used in the x4 and x8 configurations. x16-based SDRAM only has BG0.                                                                                                                                                                                                                                                                                                                                                                                                            |

| C0, C1, C2<br>(RDIMM/LRDIMM on-<br>ly) | Input | Chip ID: These inputs are used only when devices are stacked; that is, 2H, 4H, and 8H stacks for x4 and x8 configurations using through-silicon vias (TSVs). These pins are not used in the x16 configuration. Some DDR4 modules support a traditional DDP package, which uses CS1_n, CKE1, and ODT1 to control the second die. All other stack configurations, such as a 4H or 8H, are assumed to be single-load (master/slave) type configurations where C0, C1, and C2 are used as chip ID selects in conjunction with a single CS_n, CKE, and ODT. Chip ID is considered part of the command code.                                                                                                                        |

| CKx_t<br>CKx_c                         | Input | <b>Clock:</b> Differential clock inputs. All address, command, and control input signals are sampled on the crossing of the positive edge of CK_t and the negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CKEx                                   | Input | Clock enable: CKE HIGH activates and CKE LOW deactivates the internal clock signals, device input buffers, and output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH operations (all banks idle), or active power-down (row active in any bank). CKE is asynchronous for self refresh exit. After V <sub>REFCA</sub> has become stable during the power-on and initialization sequence, it must be maintained during all operations (including SELF REFRESH). CKE must be maintained HIGH throughout read and write accesses. Input buffers (excluding CK_t, CK_c, ODT, RESET_n, and CKE) are disabled during power-down. Input buffers (excluding CKE and RESET_n) are disabled during self refresh. |

| CSx_n                                  | Input | <b>Chip select:</b> All commands are masked when CS_n is registered HIGH. CS_n provides external rank selection on systems with multiple ranks. CS_n is considered part of the command code (CS2_n and CS3_n are not used on UDIMMs).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Pin Descriptions

**Table 5: Pin Descriptions (Continued)**

| Symbol                                                       | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ODTx                                                         | Input      | <b>On-die termination:</b> ODT (registered HIGH) enables termination resistance internal to the DDR4 SDRAM. When enabled, ODT ( $R_{TT}$ ) is applied only to each DQ, DQS_t, DQS_c, DM_n/DBI_n/TDQS_t, and TDQS_c signal for x4 and x8 configurations (when the TDQS function is enabled via the mode register). For the x16 configuration, $R_{TT}$ is applied to each DQ, DQSU_t, DQSU_c, DQSL_t, DQSL_c, UDM_n, and LDM_n signal. The ODT pin will be ignored if the mode registers are programmed to disable $R_{TT}$ .                                                                                                                                                                                                        |

| PARITY                                                       | Input      | Parity for command and address: This function can be enabled or disabled via the mode register. When enabled in MR5, the DRAM calculates parity with ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, BG[1:0], BA[1:0], A[16:0]. Input parity should be maintained at the rising edge of the clock and at the same time as command and address with CS_n LOW.                                                                                                                                                                                                                                                                                                                                                                                 |

| RAS_n/A16<br>CAS_n/A15<br>WE_n/A14                           | Input      | <b>Command inputs:</b> RAS_n/A16, CAS_n/A15, and WE_n/A14 (along with CS_n) define the command and/or address being entered and have multiple functions. For example, for activation with ACT_n LOW, these are addresses like A16, A15, and A14, but for a non-activation command with ACT_n HIGH, these are command pins for READ, WRITE, and other commands defined in Command Truth Table.                                                                                                                                                                                                                                                                                                                                       |

| RESET_n                                                      | CMOS Input | <b>Active LOW asynchronous reset:</b> Reset is active when RESET_n is LOW and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SAx                                                          | Input      | <b>Serial address inputs:</b> Used to configure the temperature sensor/SPD EEPROM address range on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCL                                                          | Input      | <b>Serial clock for temperature sensor/SPD EEPROM:</b> Used to synchronize communication to and from the temperature sensor/SPD EEPROM on the I <sup>2</sup> C bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DQx, CBx                                                     | I/O        | <b>Data input/output and check bit input/output:</b> Bidirectional data bus. DQ represents DQ[3:0], DQ[7:0], and DQ[15:0] for the x4, x8, and x16 configurations, respectively. If cyclic redundancy checksum (CRC) is enabled via the mode register, the CRC code is added at the end of the data burst. Any one or all of DQ0, DQ1, DQ2, or DQ3 may be used for monitoring of internal V <sub>REF</sub> level during test via mode register setting MR[4] A[4] = HIGH; training times change when enabled.                                                                                                                                                                                                                        |

| DM_n/DBI_n/<br>TDQS_t (DMU_n,<br>DBIU_n), (DML_n/<br>DBII_n) | I/O        | Input data mask and data bus inversion: DM_n is an input mask signal for write data. Input data is masked when DM_n is sampled LOW coincident with that input data during a write access. DM_n is sampled on both edges of DQS. DM is multiplexed with the DBI function by the mode register A10, A11, and A12 settings in MR5. For a x8 device, the function of DM or TDQS is enabled by the mode register A11 setting in MR1. DBI_n is an input/output identifying whether to store/output the true or inverted data. If DBI_n is LOW, the data will be stored/output after inversion inside the DDR4 device and not inverted if DBI_n is HIGH. TDQS is only supported in x8 SDRAM configurations (TDQS is not valid for UDIMMs). |

| SDA                                                          | I/O        | <b>Serial Data:</b> Bidirectional signal used to transfer data in or out of the EEPROM or EEPROM/TS combo device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DQS_t DQS_c DQSU_t DQSU_c DQSL_t DQSL_c                      | I/O        | <b>Data strobe:</b> Output with read data, input with write data. Edge-aligned with read data, centered-aligned with write data. For x16 configurations, DQSL corresponds to the data on DQ[7:0], and DQSU corresponds to the data on DQ[15:8]. For the x4 and x8 configurations, DQS corresponds to the data on DQ[3:0] and DQ[7:0], respectively. DDR4 SDRAM supports a differential data strobe only and does not support a single-ended data strobe.                                                                                                                                                                                                                                                                            |

| ALERT_n                                                      | Output     | <b>Alert output:</b> Possesses functions such as CRC error flag and command and address parity error flag as output signal. If a CRC error occurs, ALERT_n goes LOW for the period time interval and returns HIGH. If an error occurs during a command address parity check, ALERT_n goes LOW until the on-going DRAM internal recovery transaction is complete. During connectivity test mode, this pin functions as an input. Use of this signal is system-dependent. If not connected as signal, ALERT_n pin must be connected to V <sub>DD</sub> on DIMMs.                                                                                                                                                                      |

| EVENT_n                                                      | Output     | <b>Temperature event:</b> The EVENT_n pin is asserted by the temperature sensor when critical temperature thresholds have been exceeded. This pin has no function (NF) on modules without temperature sensors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Pin Descriptions

#### **Table 5: Pin Descriptions (Continued)**

| Symbol                                            | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDQS_t<br>TDQS_c<br>(x8 DRAM-based<br>RDIMM only) | Output | <b>Termination data strobe:</b> When enabled via the mode register, the DRAM device enables the same R <sub>TT</sub> termination resistance on TDQS_t and TDQS_c that is applied to DQS_t and DQS_c. When the TDQS function is disabled via the mode register, the DM/TDQS_t pin provides the data mask (DM) function, and the TDQS_c pin is not used. The TDQS function must be disabled in the mode register for both the x4 and x16 configurations. The DM function is supported only in x8 and x16 configurations. DM, DBI, and TDQS are a shared pin and are enabled/disabled by mode register settings. For more information about TDQS, see the DDR4 DRAM component data sheet (TDQS_t and TDQS_c are not valid for UDIMMs). |

| $V_{DD}$                                          | Supply | Module power supply: 1.2V (TYP).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>PP</sub>                                   | Supply | DRAM activating power supply: 2.5V -0.125V/+0.250V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>REFCA</sub>                                | Supply | Reference voltage for control, command, and address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub>                                   | Supply | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>TT</sub>                                   | Supply | Power supply for termination of address, command, and control V <sub>DD</sub> /2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DDSPD</sub>                                | Supply | Power supply used to power the I <sup>2</sup> C bus for SPD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RFU                                               | -      | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NC                                                | -      | No connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NF                                                | -      | No function: May have internal connection present, but has no function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **DQ Map**

**Table 6: Component-to-Module DQ Map**

| Component<br>Reference<br>Number | Component<br>DQ | Module DQ | Module Pin<br>Number | Component<br>Reference<br>Number | Component<br>DQ | Module DQ | Module Pin<br>Number |

|----------------------------------|-----------------|-----------|----------------------|----------------------------------|-----------------|-----------|----------------------|

| U1                               | 0               | 3         | 157                  | U2                               | 0               | 11        | 168                  |

|                                  | 1               | 1         | 150                  |                                  | 1               | 9         | 161                  |

|                                  | 2               | 2         | 12                   |                                  | 2               | 10        | 23                   |

|                                  | 3               | 0         | 5                    |                                  | 3               | 8         | 16                   |

|                                  | 4               | 7         | 155                  |                                  | 4               | 15        | 166                  |

|                                  | 5               | 5         | 148                  |                                  | 5               | 13        | 159                  |

|                                  | 6               | 6         | 10                   |                                  | 6               | 14        | 21                   |

|                                  | 7               | 4         | 3                    |                                  | 7               | 12        | 14                   |

| U3                               | 0               | 19        | 179                  | U4                               | 0               | 27        | 190                  |

|                                  | 1               | 17        | 172                  |                                  | 1               | 25        | 183                  |

|                                  | 2               | 18        | 34                   |                                  | 2               | 26        | 45                   |

|                                  | 3               | 16        | 27                   |                                  | 3               | 24        | 38                   |

|                                  | 4               | 23        | 177                  |                                  | 4               | 31        | 188                  |

|                                  | 5               | 21        | 170                  |                                  | 5               | 29        | 181                  |

|                                  | 6               | 22        | 32                   |                                  | 6               | 30        | 43                   |

|                                  | 7               | 20        | 28                   |                                  | 7               | 28        | 36                   |

| U5                               | 0               | CB3       | 201                  | U7                               | 0               | 35        | 249                  |

|                                  | 1               | CB1       | 194                  |                                  | 1               | 33        | 242                  |

|                                  | 2               | CB2       | 56                   |                                  | 2               | 34        | 104                  |

|                                  | 3               | CB0       | 49                   |                                  | 3               | 32        | 97                   |

|                                  | 4               | CB7       | 199                  |                                  | 4               | 39        | 247                  |

|                                  | 5               | CB5       | 192                  |                                  | 5               | 37        | 240                  |

|                                  | 6               | CB6       | 54                   |                                  | 6               | 38        | 102                  |

|                                  | 7               | CB4       | 47                   |                                  | 7               | 36        | 95                   |

| U8                               | 0               | 43        | 260                  | U9                               | 0               | 51        | 271                  |

|                                  | 1               | 41        | 253                  |                                  | 1               | 49        | 264                  |

|                                  | 2               | 42        | 115                  |                                  | 2               | 50        | 126                  |

|                                  | 3               | 40        | 108                  |                                  | 3               | 48        | 119                  |

|                                  | 4               | 47        | 258                  |                                  | 4               | 55        | 269                  |

|                                  | 5               | 45        | 251                  |                                  | 5               | 53        | 262                  |

|                                  | 6               | 46        | 113                  |                                  | 6               | 54        | 124                  |

|                                  | 7               | 44        | 106                  |                                  | 7               | 52        | 117                  |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM DQ Map

#### **Table 6: Component-to-Module DQ Map (Continued)**

| Component<br>Reference<br>Number | Component<br>DQ | Module DQ | Module Pin<br>Number | Component<br>Reference<br>Number | Component<br>DQ | Module DQ | Module Pin<br>Number |

|----------------------------------|-----------------|-----------|----------------------|----------------------------------|-----------------|-----------|----------------------|

| U10                              | 0               | 59        | 282                  |                                  |                 |           |                      |

|                                  | 1               | 57        | 275                  |                                  |                 |           |                      |

|                                  | 2               | 58        | 137                  |                                  |                 |           |                      |

|                                  | 3               | 56        | 130                  |                                  |                 |           |                      |

|                                  | 4               | 63        | 280                  |                                  |                 |           |                      |

|                                  | 5               | 61        | 273                  |                                  |                 |           |                      |

|                                  | 6               | 62        | 135                  |                                  |                 |           |                      |

|                                  | 7               | 60        | 128                  |                                  |                 |           |                      |

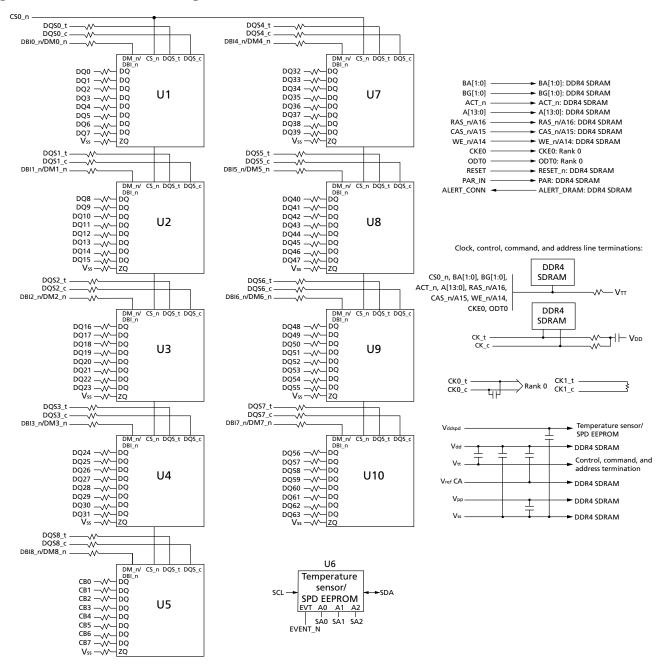

### **Functional Block Diagram**

**Figure 2: Functional Block Diagram**

Note: 1. The ZQ ball on each DDR4 component is connected to an external  $240\Omega \pm 1\%$  resistor that is tied to ground. It is used for the calibration of the component's ODT and output driver.

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM General Description

## **General Description**

High-speed DDR4 SDRAM modules use DDR4 SDRAM devices with two or four internal memory bank groups. DDR4 SDRAM modules utilizing 4- and 8-bit-wide DDR4 SDRAM devices have four internal bank groups consisting of four memory banks each, providing a total of 16 banks. 16-bit-wide DDR4 SDRAM devices have two internal bank groups consisting of four memory banks each, providing a total of eight banks. DDR4 SDRAM modules benefit from the DDR4 SDRAM's use of an 8*n*-prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single READ or WRITE operation for the DDR4 SDRAM effectively consists of a single 8*n*-bit-wide, four-clock data transfer at the internal DRAM core and eight corresponding *n*-bit-wide, one-half-clock-cycle data transfers at the I/O pins.

DDR4 modules use two sets of differential signals: DQS\_t and DQS\_c to capture data and CK\_t and CK\_c to capture commands, addresses, and control signals. Differential clocks and data strobes ensure exceptional noise immunity for these signals and provide precise crossing points to capture input signals.

### **Fly-By Topology**

DDR4 modules use faster clock speeds than earlier DDR technologies, making signal quality more important than ever. For improved signal quality, the clock, control, command, and address buses have been routed in a fly-by topology, where each clock, control, command, and address pin on each DRAM is connected to a single trace and terminated (rather than a tree structure, where the termination is off the module near the connector). Inherent to fly-by topology, the timing skew between the clock and DQS signals can be accounted for by using the write-leveling feature of DDR4.

## **Module Manufacturing Location**

Micron Technology manufactures modules at sites worldwide. Customers may receive modules from any of the manufacturing locations listed below.

**Table 7: DRAM Module Manufacturing Locations**

| Manufacturing Site Location | Country of Origin Specified on Label |

|-----------------------------|--------------------------------------|

| Boise, USA                  | USA                                  |

| Aguadilla, Puerto Rico      | Puerto Rico                          |

| Xian, China                 | China                                |

| Singapore                   | Singapore                            |

## **Address Mapping to DRAM**

#### **Address Mirroring**

To achieve optimum routing of the address bus on DDR4 multirank modules, the address bus will be wired as shown in the table below, or mirrored. For quad-rank modules, ranks 1 and 3 are mirrored, and ranks 0 and 2 are non-mirrored. Highlighted address pins have no secondary functions allowing for normal operation when crosswired. Data is still read from the same address it was written. However, LOAD MODE operations require a specific address. This requires the controller to accommodate for a rank that is mirrored. Systems may reference DDR4 SPD to determine whether the module has mirroring implemented or not. See the JEDEC DDR4 SPD specification for more details.

**Table 8: Address Mirroring**

| Edge Connector Pin | DRAM Pin, Non-Mirrored | DRAM Pin, Mirrored |

|--------------------|------------------------|--------------------|

| A0                 | A0                     | A0                 |

| A1                 | A1                     | A1                 |

| A2                 | A2                     | A2                 |

| A3                 | A3                     | A4                 |

| A4                 | A4                     | A3                 |

| A5                 | A5                     | A6                 |

| A6                 | A6                     | A5                 |

| A7                 | A7                     | A8                 |

| A8                 | A8                     | A7                 |

| A9                 | A9                     | A9                 |

| A10                | A10                    | A10                |

| A11                | A11                    | A13                |

| A13                | A13                    | A11                |

| A12                | A12                    | A12                |

| A14                | A14                    | A14                |

| A15                | A15                    | A15                |

| A16                | A16                    | A16                |

| A17                | A17                    | A17                |

| BA0                | BA0                    | BA1                |

| BA1                | BA1                    | BA0                |

| BG0                | BG0                    | BG1                |

| BG1                | BG1                    | BG0                |

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM Temperature Sensor with SPD EEPROM Operation

### **Temperature Sensor with SPD EEPROM Operation**

#### **Thermal Sensor Operations**

The integrated thermal sensor continuously monitors the temperature of the module PCB directly below the device and updates the temperature data register. Temperature data may be read from the bus host at any time, which provides the host real-time feedback of the module's temperature. Multiple programmable and read-only temperature registers can be used to create a custom temperature-sensing solution based on system requirements and JEDEC JC-42.2.

#### **EVENT\_n Pin**

The temperature sensor also adds the EVENT\_n pin (open-drain), which requires a pull-up to  $V_{DDSPD}$ . EVENT\_n is a temperature sensor output used to flag critical events that can be set up in the sensor's configuration registers. EVENT\_n is not used by the serial presence-detect (SPD) EEPROM.

EVENT\_n has three defined modes of operation: interrupt, comparator, and TCRIT. In interrupt mode, the EVENT\_n pin remains asserted until it is released by writing a 1 to the clear event bit in the status register. In comparator mode, the EVENT\_n pin clears itself when the error condition is removed. Comparator mode is always used when the temperature is compared against the TCRIT limit. In TCRIT only mode, the EVENT\_n pin is only asserted if the measured temperature exceeds the TCRIT limit; it then remains asserted until the temperature drops below the TCRIT limit minus the TCRIT hysteresis.

### **SPD EEPROM Operation**

DDR4 SDRAM modules incorporate SPD. The SPD data is stored in a 512-byte, JEDEC JC-42.4-compliant EEPROM that is segregated into four 128-byte, write-protectable blocks. The SPD content is aligned with these blocks as shown in the table below.

| Block | F                                                 | Range                                     | Description                       |  |

|-------|---------------------------------------------------|-------------------------------------------|-----------------------------------|--|

| 0     | 0–127 000h–07Fh Configuration and DRAM parameters |                                           | Configuration and DRAM parameters |  |

| 1     | 128–255                                           | 080h–0FFh                                 | Th Module parameters              |  |

| 2     | 2 256–319 100h–13Fh                               |                                           | Reserved (all bytes coded as 00h) |  |

|       | 320–383                                           | 0–383 140h–17Fh Manufacturing information |                                   |  |

| 3     | 384–511                                           | 180h–1FFh                                 | End-user programmable             |  |

The first 384 bytes are programmed by Micron to comply with JEDEC standard JC-45, "Appendix X: Serial Presence Detect (SPD) for DDR4 SDRAM Modules." The remaining 128 bytes of storage are available for use by the customer.

The EEPROM resides on a two-wire  $I^2C$  serial interface and is not integrated with the memory bus in any manner. It operates as a slave device in the  $I^2C$  bus protocol, with all operations synchronized by the serial clock. Transfer rates of up to 1 MHz are achievable at 2.5V (NOM).

Micron implements reversible software write protection on DDR4 SDRAM-based modules. This prevents the lower 384 bytes (bytes 0 to 383) from being inadvertently programmed or corrupted. The upper 128 bytes remain available for customer use and are unprotected.

#### 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM **Electrical Specifications**

### **Electrical Specifications**

Stresses greater than those listed may cause permanent damage to the module. This is a stress rating only, and functional operation of the module at these or any other conditions outside those indicated in each device's data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 9: Absolute Maximum Ratings**

| Symbol                             | Parameter                                                  | Min  | Max | Units | Notes |

|------------------------------------|------------------------------------------------------------|------|-----|-------|-------|

| $V_{DD}$                           | $V_{DD}$ supply voltage relative to $V_{SS}$               | -0.4 | 1.5 | V     | 1     |

| $V_{\rm DDQ}$                      | $V_{DDQ}$ supply voltage relative to $V_{SS}$              | -0.4 | 1.5 | V     | 1     |

| V <sub>PP</sub>                    | Voltage on V <sub>PP</sub> pin relative to V <sub>SS</sub> | -0.4 | 3.0 | V     | 2     |

| V <sub>IN</sub> , V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub>             | -0.4 | 1.5 | V     |       |

#### **Table 10: Operating Conditions**

| Symbol                 | Parameter                                                                                                         | Min                              | Nom                   | Max                           | Units | Notes |

|------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|-------------------------------|-------|-------|

| V <sub>DD</sub>        | V <sub>DD</sub> supply voltage                                                                                    | 1.14                             | 1.2                   | 1.26                          | V     | 1     |

| V <sub>PP</sub>        | DRAM activating power supply                                                                                      | 2.375                            | 2.5                   | 2.75                          | V     | 2     |

| V <sub>REFCA(DC)</sub> | Input reference voltage command/<br>address bus                                                                   | 0.49 × V <sub>DD</sub>           | 0.5 × V <sub>DD</sub> | 0.51 × V <sub>DD</sub>        | V     | 3     |

| I <sub>VTT</sub>       | Termination reference current from V <sub>TT</sub>                                                                | -750                             | _                     | 750                           | mA    |       |

| V <sub>TT</sub>        | Termination reference voltage (DC) – command/address bus                                                          | 0.49 × V <sub>DD</sub> -<br>20mV | 0.5 × V <sub>DD</sub> | 0.51 × V <sub>DD</sub> + 20mV | V     | 4     |

| I <sub>IN</sub>        | Input leakage current; any input excluding ZQ;<br>0V < V <sub>IN</sub> < 1.1V                                     | -2.0                             | _                     | 2.0                           | μΑ    | 5     |

| I <sub>ZQ</sub>        | Input leakage current; ZQ                                                                                         | -50.0                            | -                     | 10.0                          | μΑ    | 5, 6  |

| I <sub>OZpd</sub>      | Output leakage current; $V_{OUT} = V_{DD}$ ; DQ is High-Z                                                         | _                                | _                     | 10.0                          | μΑ    | 7     |

| I <sub>OZpu</sub>      | Output leakage current; V <sub>OUT</sub> = V <sub>SS</sub> ; DQ is High-Z;<br>ODT is disabled with ODT input HIGH | -50.0                            | _                     | _                             | μΑ    | 7     |

| I <sub>VREFCA</sub>    | $V_{REFCA}$ leakage; $V_{REFCA} = V_{DD}/2$ (after DRAM is initialized)                                           | -2.0                             | _                     | 2.0                           | μΑ    | 5     |

- Notes: 1.  $V_{DDQ}$  tracks with  $V_{DD}$ ;  $V_{DDQ}$  and  $V_{DD}$  are tied together.

- 2.  $V_{PP}$  must be greater than or equal to  $V_{DD}$  at all times.

- 3.  $V_{REFCA}$  must not be greater than 0.6 x  $V_{DD}$ . When  $V_{DD}$  is less than 500mV,  $V_{REF}$  may be less than or equal to 300mV.

- 4.  $V_{TT}$  termination voltages in excess of the specification limit adversely affect the voltage margins of command and address signals and reduce timing margins.

- 5. Multiply by the number of DRAM die on the module.

- 6. Tied to ground. Not connected to edge connector.

- 7. Multiply by the number of module ranks and then times the number of die per package.

#### 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM **Electrical Specifications**

#### **Table 11: Thermal Characteristics**

| Symbol            | Parameter/Condition                                      | Value      | Units   | Notes      |

|-------------------|----------------------------------------------------------|------------|---------|------------|

| T <sub>C</sub>    | Commercial operating case temperature                    | 0 to 85    | °C      | 1, 2, 3    |

| T <sub>C</sub>    |                                                          | >85 to 95  | °C      | 1, 2, 3, 4 |

| T <sub>OPER</sub> | Normal operating temperature range                       | 0 to 85    | °C      | 5, 7       |

| T <sub>OPER</sub> | Extended temperature operating range (optional)          | >85 to 95  | °C      | 5, 7       |

| T <sub>STG</sub>  | Non-operating storage temperature                        | -55 to 100 | °C      | 6          |

| RH <sub>STG</sub> | Non-operating storage relative humidity (non-condensing) | 5 to 95    | %       |            |

| NA                | Change rate of storage temperature                       | 20         | °C/hour |            |

- Notes: 1. Maximum operating case temperature; T<sub>C</sub> is measured in the center of the package.

- 2. A thermal solution must be designed to ensure the DRAM device does not exceed the maximum T<sub>C</sub> during operation.

- 3. Device functionality is not guaranteed if the DRAM device exceeds the maximum T<sub>C</sub> during operation.

- 4. If T<sub>C</sub> exceeds 85°C, the DRAM must be refreshed externally at 2X refresh, which is a 3.9µs interval refresh rate.

- 5. The refresh rate must double when  $85^{\circ}\text{C} < T_{OPER} \le 95^{\circ}\text{C}$ .

- 6. Storage temperature is defined as the temperature of the top/center of the DRAM and does not reflect the storage temperatures of shipping trays.

- 7. For additional information, refer to technical note TN-00-08: "Thermal Applications" available at micron.com.

## 8GB (x72, ECC, SR) 288-Pin DDR4 VLP UDIMM DRAM Operating Conditions

### **DRAM Operating Conditions**

Recommended AC operating conditions are given in the DDR4 component data sheets. Component specifications are available at micron.com. Module speed grades correlate with component speed grades, as shown below.

#### **Table 12: Module and Component Speed Grades**

DDR4 components may exceed the listed module speed grades; module may not be available in all listed speed grades

| Module Speed Grade | Component Speed Grade |

|--------------------|-----------------------|

| -3G2               | -062E                 |

| -2 <b>G</b> 9      | -068                  |

| -2G6               | -075                  |

| -2G3               | -083                  |

| -2G1               | -093E                 |

#### **Design Considerations**

#### **Simulations**

Micron memory modules are designed to optimize signal integrity through carefully designed terminations, controlled board impedances, routing topologies, trace length matching, and decoupling. However, good signal integrity starts at the system level. Micron encourages designers to simulate the signal characteristics of the system's memory bus to ensure adequate signal integrity of the entire memory system.

#### **Power**

Operating voltages are specified at the edge connector of the module, not at the DRAM. Designers must account for any system voltage drops at anticipated power levels to ensure the required supply voltage is maintained.

#### I<sub>DD</sub>, I<sub>PP</sub>, and I<sub>DDO</sub> Specifications

$I_{DD}$  and  $I_{PP}$  values are only for the DDR4 SDRAM and are calculated from values in the supporting component data sheet.  $I_{PP}$  and  $I_{DDQ}$  currents are not included in  $I_{DD}$  currents.  $I_{DD}$  and  $I_{DDQ}$  currents are not included in  $I_{PP}$  currents. Micron does not specify  $I_{DDQ}$  currents. In DRAM module application,  $I_{DDQ}$  cannot be measured separately because  $V_{DD}$  and  $V_{DDO}$  use a merged power layer in the module PCB.

Certain  $I_{DD}/I_{PP}$  conditions must be derated for optional modes of operation, such as CA parity, DBI, write CRC, additive latency, geardown, CAL, 2X and 4X REF, and DLL disabled. Refer to the base device data sheet  $I_{DD}$  and  $I_{PP}$  specification tables for derating values for the applicable die revision.

## **I<sub>DD</sub> Specifications**

### Table 13: DDR4 I<sub>DD</sub> Specifications and Conditions – 8GB (Die Revision B)

Values are for the MT40A1G8 DDR4 SDRAM only and are computed from values specified in the 8Gb (1 Gig x 8) component data sheet

| Parameter                                                            | Symbol             | 2666 | Units |

|----------------------------------------------------------------------|--------------------|------|-------|

| One bank ACTIVATE-PRECHARGE current                                  | I <sub>DD0</sub>   | 459  | mA    |

| One bank ACTIVATE-PRECHARGE, wordline boost, I <sub>PP</sub> current | I <sub>PP0</sub>   | 27   | mA    |