# **16Gb DDR5 SDRAM Addendum**

# MT60B4G4, MT60B2G8, MT60B1G16 Die Revision G

# Features

This document describes the product specifications that are unique to Micron 16Gb DDR5 Die Revision G device. For general Micron DDR5 SDRAM specifications, see the Micron DDR5 SDRAM Core Product Data Sheet. Content in this 16Gb Die Revision G DDR5 SDRAM data sheet addendum supersedes content defined in the core data sheet.

- $V_{DD} = V_{DDO} = 1.1V$  (NOM)

- $V_{PP} = 1.8V$  (NOM)

- On-die, internal, adjustable  $V_{REF}$  generation for DQ, CA, CS

- 1.1V pseudo open-drain I/O

- TC maximum up to 95°C

- 32ms, 8192-cycle refresh up to 85°C

- 16ms, 8192-cycle refresh at >85°C to 95°C

- 32 internal banks (x4, x8): 8 groups of 4 banks each

- 16 internal banks (x16): 4 groups of 4 banks each

- 16n-bit prefetch architecture

- 1 cycle/2 cycle command structure

- 2N mode

- All bank and same bank refresh

- Multi-purpose command (MPC)

- CS/CA training mode

- On-die ECC (bounded fault)

- ECC transparency and error scrub

- Decision feedback equalization (DFE)

- Loopback mode

- Command-based non-target (NT) nominal, DQ/DQS park, and dynamic WR on-die termination (ODT)

- sPPR and hPPR capability

- Per-DRAM addressability

- JEDEC JESD-79.5 compliant

| Options <sup>1</sup>                       | Marking |

|--------------------------------------------|---------|

| Configuration                              |         |

| – 4 Gig x 4                                | 4G4     |

| – 2 Gig x 8                                | 2G8     |

| – 1 Gig x 16                               | 1G16    |

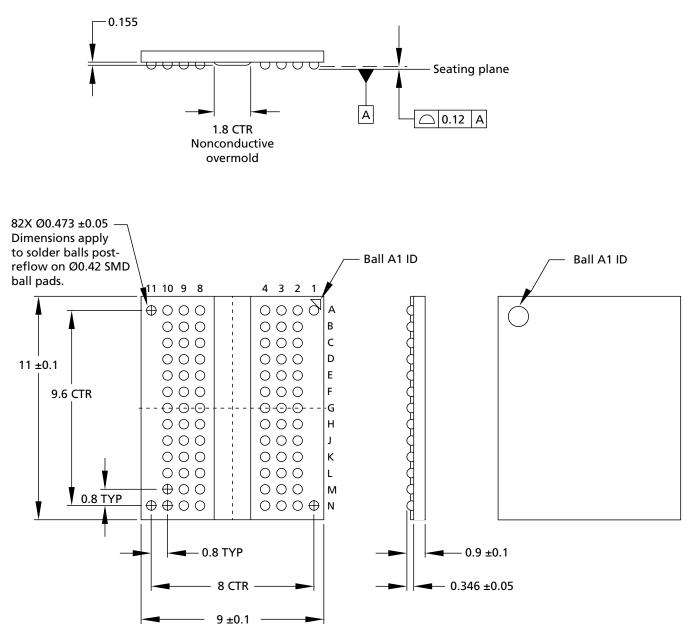

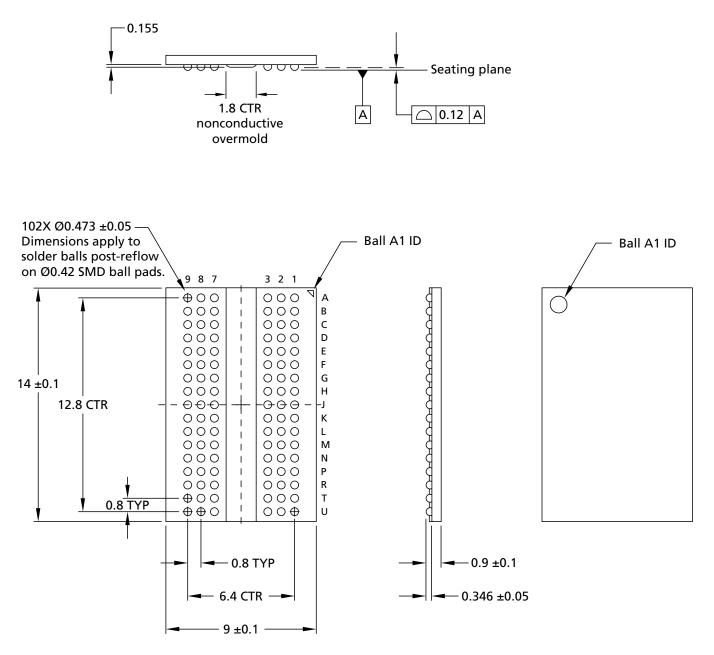

| • FBGA SDP Packages (Pb-free)              |         |

| – x4, x8 82-ball (9mm x 11mm)              | HB      |

| – x16 102-ball (9mm x 14mm)                | HC      |

| • Timing – cycle time                      |         |

| – 0.384ns @ CL = 42                        | -52B    |

| -0.357ns @ CL = 46                         | -56B    |

| <ul> <li>Operating temperature</li> </ul>  |         |

| – Commercial (0°C < T <sub>C</sub> < 95°C) | None    |

| – Industrial (–40°C < $T_C$ < 95°C)        | IT      |

| Die Revision                               | :G      |

Notes: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on micron.com for available offerings.

#### Table 1: 16Gb Addressing

| Configuration   |                                                                      | 4Gb x4       | 2Gb x8       | 1Gb x16      |

|-----------------|----------------------------------------------------------------------|--------------|--------------|--------------|

| Bank<br>address | Number of bank groups/number of banks per bank group/number of banks | 8/4/32       | 8 / 4 / 32   | 4/4/16       |

|                 | Bank group address                                                   | BG0-BG2      | BG0-BG2      | BG0-BG1      |

|                 | Bank address in a bank group                                         | BA0-BA1      | BA0-BA1      | BA0-BA1      |

| Row add         | ress                                                                 | R0-R15       | R0-R15       | R0-R15       |

| Column a        | ddress                                                               | C0-C10       | C0-C9        | C0-C9        |

| Page size       |                                                                      | 1KB          | 1KB          | 2KB          |

| Chip IDs/r      | maximum stack height                                                 | CID0-3 / 16H | CID0-3 / 16H | CID0-3 / 16H |

#### **Table 2: Part Numbers and Timing Parameters**

| Part Number          | Configuration | Memory<br>Clock/<br>Data Rate | Clock Cycles<br>(CL- <sub>n</sub> RCD- <sub>n</sub> RP) | <sup>t</sup> AA<br>(ns) | <sup>t</sup> RCD<br>(ns) | <sup>t</sup> RP<br>(ns) | Designation <sup>1</sup> |

|----------------------|---------------|-------------------------------|---------------------------------------------------------|-------------------------|--------------------------|-------------------------|--------------------------|

| MT60B4G4HB-52B:G     | 4Gb x4        | 0.384ns/<br>5200 MT/s         | 42-42-42                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B2G8HB-52B:G     | 2Gb x8        | 0.384ns/<br>5200 MT/s         | 42-42-42                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B1G16HC-52B:G    | 1Gb x16       | 0.384ns/<br>5200 MT/s         | 42-42-42                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B2G8HB-52B IT:G  | 2Gb x8        | 0.384ns/<br>5200 MT/s         | 42-42-42                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B1G16HC-52B IT:G | 1Gb x16       | 0.384ns/<br>5200 MT/s         | 42-42-42                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B4G4HB-56B:G     | 4Gb x4        | 0.357ns/<br>5600 MT/s         | 46-45-45                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B2G8HB-56B:G     | 2Gb x8        | 0.357ns/<br>5600 MT/s         | 46-45-45                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B1G16HC-56B:G    | 1Gb x16       | 0.357ns/<br>5600 MT/s         | 46-45-45                                                | 16.000                  | 16.000                   | 16.000                  | Production               |

| MT60B2G8HB-56B IT:G  | 2Gb x8        | 0.357ns/<br>5600 MT/s         | 46-45-45                                                | 16.000                  | 16.000                   | 16.000                  | Preliminary              |

| MT60B1G16HC-56B IT:G | 1Gb x16       | 0.357ns/<br>5600 MT/s         | 46-45-45                                                | 16.000                  | 16.000                   | 16.000                  | Preliminary              |

Notes: 1. **Production**: Although considered final, these specifications are subject to change as further product development and data characterization sometimes occur. **Preliminary**: For evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications. **Advance**: Contains initial descriptions of products still under development. For evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications.

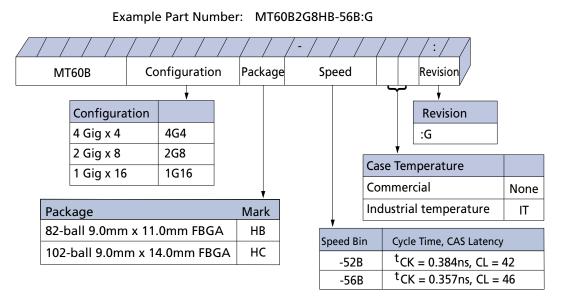

#### Figure 1: Order Part Number Example

# **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly or indirectly, any claim of product is a sutomotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

**Critical Applications.** Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

**Customer Responsibility.** Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAILURE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

# General Notes and Functional Block Diagrams

# **General Notes**

- The functionality and the timing specifications discussed in this data sheet are for the DLL enable mode of operation (normal operation), unless specifically stated otherwise.

- Throughout the data sheet, the various figures and text refer to DQs as "DQ." The DQ term is to be interpreted as any and all DQ collectively, unless specifically stated otherwise.

- The terms "\_t" and "\_c" are used to represent the true and complement of a differential signal pair. These terms replace the previously used notation of "#" and/or over-bar characters. For example, differential data strobe pair DQS, DQS# is now referred to as DQS\_t, DQS\_c.

- The term "\_n" is used to represent a signal that is active LOW and replaces the previously used "#" and/or overbar characters. For example: CS# is now referred to as CS\_n.

- The terms "DQS" and "CK" found throughout the data sheet are to be interpreted as DQS\_t, DQS\_c and CK\_t, CK\_c respectively, unless specifically stated otherwise.

- Complete functionality may be described throughout the entire document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- Any specific requirement takes precedence over a general statement.

- Any functionality not specifically stated here within is considered undefined, illegal, and not supported, and can result in unknown operation.

- Addressing is denoted as BG[n] for bank group, BA[n] for bank address, and A[n] for row/col address.

- A NOP is considered a valid command for very specific states such as power-down exit, self-refresh exit, and reset. The NOP must satisfy any associated command timings with respect to the preceding valid command.

- Not all features described within this document may be available on the Rev. A (first) version.

- Not all specifications listed are finalized industry standards; best conservative estimates have been provided when an industry standard has not been finalized.

- Although it is implied throughout the specification, the DRAM must be used after reaching a stable power-on level, which is achieved by following the proper voltage ramp and power-up initialization sequence procedures as outline in this specification.

- Not all features designated in the data sheet may be supported by earlier die revisions due to late definition by JEDEC.

# **Definitions of the Device-Pin Signal Level**

- HIGH: A device pin is driving the logic 1 state.

- LOW: A device pin is driving the logic 0 state.

- High-Z or (HI-Z/Hi-Z): A device pin is tri-state

- ODT: A device pin terminates with the ODT settings, which could be terminating or tri-state depending on the mode register settings.

# **Definitions of the Bus Signal Level**

- HIGH: One device on the bus is HIGH, and all other devices on the bus are either ODT or High-Z. The voltage level on the bus is nominally  $V_{\rm DDQ}$ .

- LOW: One device on the bus is LOW, and all other devices on the bus are either ODT or High-Z. The voltage level on the bus is nominally  $V_{OL(DC)}$  if ODT was enabled, or  $V_{SSQ}$  if High-Z.

- High-Z or (HI-Z/Hi-Z): All devices on the bus are High-Z. The voltage level on the bus is undefined as the bus is floating.

- ODT: At least one device on the bus is ODT, and all others are High-Z. The voltage level on the bus is nominally  $V_{DDQ}$ .

- The specification requires 8,192 refresh commands within 32ms between 0°C and 85°C. This allows for a <sup>t</sup>REFI of 3.9µs in normal refresh mode. The specification also requires 8,192 refresh commands within 16ms between 85°C and 95°C. This allows for a <sup>t</sup>REFI of 1.95µs in normal refresh mode.

# **Industrial Temperature**

An industrial temperature (IT) device option requires that the case temperature not exceed below  $-40^{\circ}$ C or above 95°C. JEDEC specifications require the refresh rate to double when T<sub>C</sub> exceeds 85°C; this also requires use of the high-temperature self-refresh option. Additionally, ODT resistance and the input/output impedance must be derated when operating outside of the commercial temperature range, when T<sub>C</sub> is between  $-40^{\circ}$ C and  $0^{\circ}$ C.

# **Automotive Temperature**

The automotive temperature (AT) device option requires that the case temperature not exceed below  $-40^{\circ}$ C or above 105°C. The specifications require the refresh rate to 2X when T<sub>C</sub> exceeds 85°C; 4X when T<sub>C</sub> exceeds 95°C. Additionally, ODT resistance and the input/output impedance must be derated when operating temperature Tc <0°C.

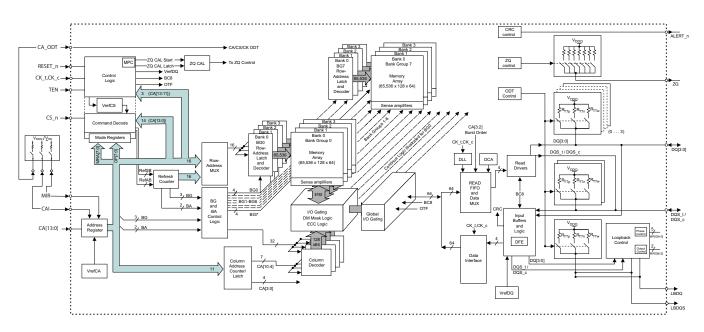

#### Figure 2: 4 Gig x4 Functional Block Diagram

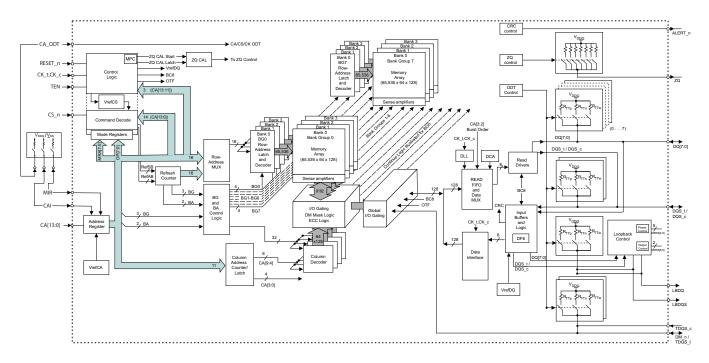

### Figure 3: 2 Gig x8 Functional Block Diagram

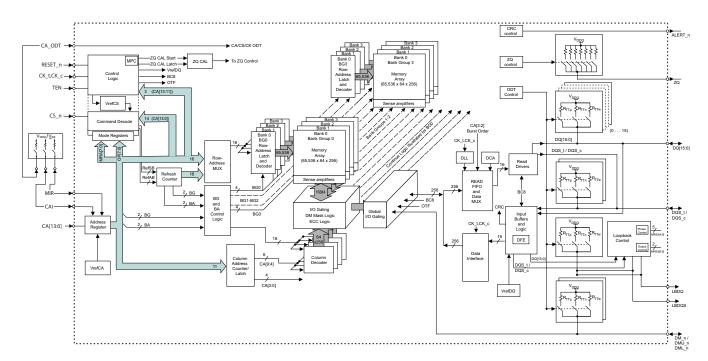

### Figure 4: 1 Gig x16 Functional Block Diagram

# **DDR5 Function Matrix**

DDR5 SDRAM has several features supported by configuration width, by density, by speed and by device die Rev. The following table is the summary of the features supported by 16Gb Die Revision G by configuration width. The functional matrix will be defined in each device-specific data sheet; therefore, device, speed and density options will vary by device data sheet.

| Function                             | <b>x4</b> | x8 | x16 | MR Default State      | Notes |

|--------------------------------------|-----------|----|-----|-----------------------|-------|

| JEDEC Mandatory                      |           |    |     |                       |       |

| BC8 OTF                              | V         | V  | V   |                       |       |

| TDQS                                 |           | V  |     |                       |       |

| Data Mask (DM)                       |           | V  | V   |                       |       |

| Data Output Disable                  | V         | V  | V   |                       |       |

| Connectivity Test Mode (CT)          | V         | V  | V   |                       |       |

| CA/CS/CK ODT                         | V         | V  | V   |                       |       |

| 2N Mode                              | V         | V  | V   |                       |       |

| Per DRAM Addressability (Enum)       | V         | V  | V   |                       |       |

| Mode Register Read (MRR)             | V         | V  | V   |                       |       |

| Mode Register Write (MRW)            | V         | V  | V   |                       |       |

| Multi-Purpose Command (MPC)          | V         | V  | V   |                       |       |

| ZQ calibration                       | V         | V  | V   |                       |       |

| CA Vref Training                     | V         | V  | V   |                       |       |

| CS Vref Training                     | V         | V  | V   |                       |       |

| DQ Vref Training                     | V         | V  | V   |                       |       |

| CS Training Mode (CSTM)              | V         | V  | V   |                       |       |

| CA Training Mode (CATM)              | V         | V  | V   |                       |       |

| Write Leveling Training              | V         | V  | V   |                       |       |

| DQS Interval Oscillator              | V         | V  | V   |                       |       |

| Read Training Pattern Mode (LFSR)    | V         | V  | V   |                       |       |

| Write Pattern Command                | V         | V  | V   |                       |       |

| Duty Cycle Adjuster (DCA) I          | V         | V  | V   | MR42:OP[1:0] = 01 (R) | 1     |

| Loopback Mode                        | V         | V  | V   |                       |       |

| Decision Feedback Equalization (DFE) | V         | V  | V   |                       |       |

| WRITE CRC                            | V         | V  | V   |                       |       |

| READ CRC                             | V         | V  | V   |                       |       |

| Programmable Preamble                | V         | V  | V   |                       |       |

| Programmable Postamble               | V         | V  | V   |                       |       |

| sPPR                                 | V         | V  | V   |                       |       |

| hPPR                                 | V         | V  | V   |                       |       |

| PPR using DQ[3:0] only               | V         | V  | V   |                       |       |

#### Table 3: DDR5 Function Matrix - 16Gb Die Rev. G. V: Supported, Blank: Not Supported (Continued)

| Function                                | <b>x4</b> | x8 | x16 | MR Default State        | Notes |

|-----------------------------------------|-----------|----|-----|-------------------------|-------|

| On-Die-ECC                              | V         | V  | V   |                         |       |

| ECC Transparency and Error Scrub        | V         | V  | V   |                         |       |

|                                         |           |    |     | MR58:OP[0] = 0 (R)      | 2     |

|                                         |           |    |     | MR58:OP[7:5] = 110 (R)  |       |

| Refresh Management (RFM)                | V         | V  | V   | MR58:OP[4:1] = 1010 (R) | 3     |

|                                         |           |    |     | MR59:OP[7:6] = 00 (R)   |       |

| Fine Granularity Refresh (FGR)          | V         | V  | V   |                         |       |

| Same Bank Refresh                       | V         | V  | V   |                         |       |

| Same Bank Precharge                     | V         | V  | V   |                         |       |

| Maximum power saving mode (MPSM)        | V         | V  | V   |                         |       |

| CS Geardown(>= 7200 MT/s)               |           |    |     |                         | 4     |

| JEDEC Optional                          |           |    |     |                         |       |

| MR65-MR69 Serial Number                 |           |    |     | MR65 - MR69 = 0x00 (R)  |       |

| BL32                                    |           |    |     |                         |       |

| BL32 OTF                                |           |    |     |                         |       |

| WICA 1/2 step                           | V         | V  | V   |                         |       |

| Duty Cycle Adjuster (DCA) II            |           |    |     | MR42:OP[7] = 0 (SR)     |       |

| MBIST/mPPR                              |           |    |     | MR23:OP[4] = 0 (SR)     |       |

| sPPR undo/lock                          | V         | V  | V   | MR23:OP[2] = 1 (SR)     |       |

| Adaptive RFM                            |           |    |     |                         |       |

| Directed DEM                            |           |    |     | MR59:OP[0] = 0 (SR)     |       |

| Directed RFM                            |           |    |     | MR59:OP[3] = 0 (R)      | 5     |

| Package output driver test mode (PODTM) |           |    |     | MR5:OP[3] = 0 (R)       |       |

| Partial array self refresh (PASR)       |           |    |     | MR19:OP[7] = 0 (R)      |       |

| Refresh interval rate (RIR)             |           |    |     | MR4:OP[3] = 0 (SR)      |       |

| Rx CTLE (CS_n, CA, DQS)                 | V         | V  | V   | M22:OP[3] = 1 (R)       |       |

| MR4 wide range refresh rate support     | V         | V  | V   | MR4:OP[5] = 1 (R)       |       |

| Test Mode MR (MR9)                      |           |    |     |                         | 6     |

| ECS Writeback Suppression               | V         | V  | V   |                         |       |

| x4 RMW Suppression                      | V         |    |     |                         |       |

Notes: 1. Device supports DCA for single/two-phase internal clock(s).

2. RFM not required.

- 3. RAAMMT, RAAIMT, and RAA counter decrement are only applicable if the RFM requirement bit is set to 1 (MR58:OP[0]=1) or ARFM is set to level A, B, or C.

- 4. Data rates of >=7200 MT/s are not supported on this die revision.

- 5. BRC support level (MR59:OP[3]) is only applicable if DRFM Enable status read bit is set to 1 (MR59:OP[0]=1)

- 6. Test Mode (TM) is a vendor-specific mode register; not used by Micron.

# **DDR5 Package Pinout and Assignments**

#### Rows

The x4/x8 device has 13 electrical rows of balls. The x16 device has 17 electrical rows of balls. Electrical is defined as rows that contain signal ball or power/ground balls. Additional rows of inactive balls may be available for mechanical support.

# **Ball Pitch**

The device uses a ball pitch of 0.8mm x 0.8mm.

### Columns

The number of depopulated columns is 3.

The device has six electrical columns of balls in two sets of three columns. Between the electrical columns are three columns where no balls are populated. Electrical is defined as columns that contain signal ball or power/ground balls. Additional columns of inactive balls may be available for mechanical support.

# 16Gb DDR5 SDRAM Die Rev G DDR5 Package Pinout and Assignments

#### Figure 5: x4/x8 Ballout Using MO-210-AN – 82-Ball

|   | 1                                             | 2                                          | 3                        | 4                              | 5 | 6 | 7  | 8                              | 9                      | 10                                         | 11  |   |

|---|-----------------------------------------------|--------------------------------------------|--------------------------|--------------------------------|---|---|----|--------------------------------|------------------------|--------------------------------------------|-----|---|

| А |                                               | ())<br>LBDQ                                | ()<br>V <sub>ss</sub>    | ())<br>V <sub>PP</sub>         |   |   |    | )<br>ZQ                        | ()<br>V <sub>SS</sub>  |                                            |     | A |

| в |                                               |                                            | ()<br>V <sub>DDQ</sub>   |                                |   |   |    | O<br>DQ3                       | ()<br>V <sub>DDQ</sub> | $\langle \rangle$                          |     | в |

| с |                                               |                                            |                          | (_)<br>DQS_t                   |   |   |    | $\langle \cdot \rangle$        | $\bigcirc$             | V <sub>DD</sub>                            |     | с |

| D |                                               | ()                                         | ()                       | ()<br>DQS_c                    |   |   | NF | F/DM_n/TDQ                     | 1                      | V <sub>SS</sub>                            |     | D |

| Е |                                               | V <sub>DDQ</sub>                           | V <sub>SS</sub>          | $\bigcirc$                     |   |   |    |                                | $\bigcirc$             | V <sub>DDQ</sub>                           |     | E |

| F |                                               | V <sub>DD</sub>                            | ()                       | NF,DQ6                         |   |   |    | NF,DQ7                         | ()                     | $\left( \right)$                           |     | F |

| G |                                               | V <sub>ss</sub>                            | V <sub>DDQ</sub>         | V <sub>SS</sub>                |   |   |    | V <sub>SS</sub><br>())<br>CK_t | V <sub>DDQ</sub>       | V <sub>SS</sub>                            |     | G |

| н |                                               | A_ODT                                      | ()                       | V <sub>DD</sub><br>())<br>CS_n |   |   |    | CK_t                           | ()                     | ()                                         |     | н |

| J |                                               | ()                                         | N V <sub>SS</sub><br>CA4 |                                |   |   |    | CA1                            | V <sub>SS</sub><br>CA5 | V <sub>DD</sub>                            |     | J |

| к |                                               | V <sub>DDQ</sub><br>())<br>V <sub>DD</sub> | CA4<br>CA6               | $\bigcirc$                     |   |   |    |                                | CA3<br>CA7             | V <sub>DDQ</sub><br>())<br>V <sub>DD</sub> |     | к |

| L |                                               | V <sub>DD</sub><br>())<br>V <sub>DDQ</sub> | ()                       | CĀ2                            |   |   |    | $\bigcirc$                     | $\left( \right)$       | $\left( \right)$                           |     | L |

| м |                                               |                                            | V <sub>ss</sub>          | CĂ8                            |   |   |    | ČĂ9                            | V <sub>ss</sub>        | V <sub>DDQ</sub>                           |     | м |

| N | $\left( \begin{array}{c} \end{array} \right)$ | ()                                         |                          |                                |   |   |    | CA13                           | ()                     | REŠĒT_n                                    | ()  | N |

|   | DNU                                           | V <sub>DD</sub>                            | V <sub>SS</sub>          | V <sub>DD</sub>                |   |   |    | V <sub>PP</sub>                | V <sub>SS</sub>        | V <sub>DD</sub>                            | DNU |   |

- Notes: 1. Additional columns and rows of inactive balls in MO-210-AN terminal pattern (x4/x8) with support balls are for mechanical support only and should not be tied electrically high or low.

- 2. Some of the additional support balls can be selectively populated at the suppliers' discretion.

- 3. DQ4-DQ7 higher-order DQ pins are connected but not used in the x4 configuration.

- 4. DM, TDQS\_t and TDQS\_c are not valid for the x4 configuration.

- 5. A comma "," separates the configuration. A slash "/" defines a mode register-selectable function, command/address function, density or package dependence.

#### Figure 6: x16 Ballout Using MO-210-AT -102 Ball

|   | 1                                                                                                                        | 2                                                                                              | 3                                                       | 4 | 5 | 6 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                                                                                      | 9                                 |   |

|---|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---|

| А |                                                                                                                          | ())<br>Vee                                                                                     |                                                         |   |   |   | )<br>ZQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ())<br>Vee                                                                                                             | ())<br>LBDQS                      | А |

| в |                                                                                                                          | V <sub>SS</sub>                                                                                | DQU2                                                    |   |   |   | DQU3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub>                                                                                                        |                                   | В |

| С |                                                                                                                          |                                                                                                | ()<br>DQSU_t                                            |   |   |   | ()<br>DMU_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                        |                                   | с |

| D | $()_{V_{SS}}()_{V_{DD}}()_{V_{DD}}()_{V_{DD}}()_{V_{DD}}()_{V_{SS}}()$                                                   |                                                                                                | DQSU_c                                                  |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        | V <sub>SS</sub>                   | D |

| Е | V DDQ                                                                                                                    | $() \\ v_{ss} \\ DQU4 \\ () \\ v_{DDQ} \\ DQL0 \\ () \\ () \\ () \\ () \\ () \\ () \\ () \\ ($ | DQ30_C                                                  |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $() \\ v_{ss} \\ \bigcirc \\ DQU5 \\ () \\ v_{DDQ} \\ \bigcirc \\ DQL1 \\ () \\ () \\ () \\ () \\ () \\ () \\ () \\ ($ | V <sub>DDQ</sub>                  | Е |

| F |                                                                                                                          |                                                                                                | DQ08<br>DQL2                                            |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        | V <sub>DD</sub>                   | F |

| G |                                                                                                                          |                                                                                                |                                                         |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                        | V <sub>DD</sub>                   | G |

| н | V <sub>SS</sub>                                                                                                          |                                                                                                | DQSL_t                                                  |   |   |   | DML_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                        | V <sub>ss</sub>                   | н |

| J | V <sub>DDQ</sub>                                                                                                         |                                                                                                | DQSL_c                                                  |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>ss</sub>                                                                                                        | V <sub>DDQ</sub>                  | J |

| к |                                                                                                                          |                                                                                                | DQSL_t<br>()<br>DQSL_c<br>DQL6<br>()<br>V <sub>SS</sub> |   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>SS</sub><br>DQL5                                                                                                | V <sub>DD</sub>                   | к |

| L | $\begin{array}{c} & & \\ & V_{DD} \\ & & \\ & & \\ & & \\ & V_{SS} \\ & & \\ & & \\ & & \\ & & \\ & CA\_ODT \end{array}$ | V <sub>DDQ</sub>                                                                               | $\langle \rangle$                                       |   |   |   | $(\bigcirc_{RFU} U \bigcirc_{DQU7} U \bigcirc_{DQU3} (\bigcirc_{DML} u ) \cap_{RFU} (\bigcirc_{DQL7} U ) \cap_{SSU} (\bigcirc_{CK} u ) \cap_{CK} U ) \cap_{CK} (\bigcirc_{CK} u ) \cap_{CK} U ) \cap_{CK} (\bigcirc_{CK} u ) \cap_{CK} U ) \cap_{CK$ | $ \begin{array}{c} V_{DDQ} \\ () \\ V_{DDQ} \\ () \\ V_{ss} \\ CA5 \end{array} $                                       |                                   | L |

| М | CA_ODT                                                                                                                   | MIR<br>()<br>V <sub>SS</sub>                                                                   | V <sub>DD</sub><br>()<br>CS_n                           |   |   |   | CK_t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DDQ</sub>                                                                                                       | TEN                               | М |

| N |                                                                                                                          | V <sub>SS</sub><br>CA4                                                                         | CS_n<br>CA0                                             |   |   |   | CK_c<br>CA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V <sub>ss</sub>                                                                                                        |                                   | N |

| Ρ |                                                                                                                          | CA4<br>CA6                                                                                     | CA0<br>CA2                                              |   |   |   | CA1<br>CA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CA5<br>CA7                                                                                                             | ()                                | Р |

| R | V <sub>DD</sub>                                                                                                          | CA6                                                                                            | CA2<br>CA8                                              |   |   |   | CA3<br>CA9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\langle \rangle$                                                                                                      | Ŷ <sub>DD</sub>                   | R |

| т | V <sub>DDQ</sub>                                                                                                         | V <sub>SS</sub><br>CA10                                                                        | CÃ8<br>()<br>CA12                                       |   |   |   | CÃ9<br>()<br>CA13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>SS</sub>                                                                                                        | V <sub>DDQ</sub><br>()<br>REŠET_n | т |

| U | ČÁÍ<br>()                                                                                                                | CA10                                                                                           | CA12                                                    |   |   |   | CA13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CA11                                                                                                                   | REŠÉT_n                           | U |